mhjedaboard

Newbie level 4

- Joined

- Sep 23, 2011

- Messages

- 6

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Location

- Iran-Teharan

- Activity points

- 1,322

Salaam every body,

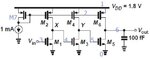

this is the circuit:

========================

I wrote these lines for the circuit:

=========================

from ".lis" output file, the operation currents are:

======================

my first problem is that why id3 is more than 1ma ?

there should be 1ma for every transistor because of current mirrors.

this is the circuit:

========================

I wrote these lines for the circuit:

Code:

.prot

.lib 'mm018.l' TT

.unprot

Vdd 1 0 DC 1.8V

Ibias 2 0 dc 1ma

Cout 6 0 100ff

M2 4 2 1 PMOS L=0.18u W=4u

M4 5 2 1 PMOS L=0.18u W=30u

M6 6 2 1 PMOS L=0.18u W=45u

M7 2 2 1 PMOS L=0.18u W=45u

M1 4 3 0 NMOS L=0.18u W=4u

M3 5 4 0 NMOS L=0.18u W=45u

M5 6 5 0 NMOS L=0.18u W=30u

.op

.OPTION CAPTAB

.prob

.end=========================

from ".lis" output file, the operation currents are:

| element | m2 | m4 | m6 | m7 | m1 | m3 | m5 |

| model | pmos.6 | pmos.3 | pmos.3 | pmos.3 | nmos.6 | nmos.3 | nmos.3 |

| region | Linear | Saturati | Linear | Saturati | Cutoff | Linear | Cutoff |

| id | -99.1687u | -1.279m | -1.046m | -1.648m | 58.7580p | 1.2795m | 845.2648p |

======================

my first problem is that why id3 is more than 1ma ?

there should be 1ma for every transistor because of current mirrors.