MammPp

Junior Member level 2

Hi all,

I tried to use HSPICE to simulate the regular PMOS circuit,

However, my problem is, why does source voltage is equal to 1V when gate voltage is equal to 1V.

The following is my code

Thank you so much for your help

Best

PJ

Test

.include 'PMOS 45nm.txt'

.param Vd = 1V

Vsupply 1 0 Vd

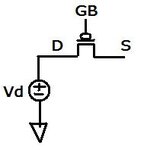

Mp D Gb S 1 PMOS L=0.25u W=1u

Vd D 0 DC Vd

Vin Gb 0 pulse (Vd 0 step 0.001ns 0.001ns step 'step*2')

.PARAM step = 300ns

.tran 1ns 'step*3'

.option post = 2

.op

.end

I tried to use HSPICE to simulate the regular PMOS circuit,

However, my problem is, why does source voltage is equal to 1V when gate voltage is equal to 1V.

The following is my code

Thank you so much for your help

Best

PJ

Test

.include 'PMOS 45nm.txt'

.param Vd = 1V

Vsupply 1 0 Vd

Mp D Gb S 1 PMOS L=0.25u W=1u

Vd D 0 DC Vd

Vin Gb 0 pulse (Vd 0 step 0.001ns 0.001ns step 'step*2')

.PARAM step = 300ns

.tran 1ns 'step*3'

.option post = 2

.op

.end