fra93

Newbie level 4

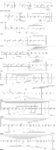

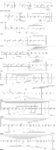

Hi I invented a "shift register" like circuit that behaves similarly to a linear feedback shift register, but it has a complete sequence.

From here on I will call this circuit Non-Linear Pseudo Random Generator NLPRG for simplicity.

Below some circuit typologies ranging from 3 up to 16 bits ( if you somebody wants I can explain how it works and provide the Verilog an C code ).

I tested all the NLPRG sequences with a counter. For example in the 16 bits case, both of them are initialized with 0x0000, any number would work. If the counter or the NLPRG reaches the number 0x0000, than end the simulation. If at the end of the simulation, both the counter and the nlprg are in the 0x0000 state than the sequence of the nlprg is complete.

But this approach does not scale up because the simulation time increases exponentially with the number of bits.

Can somebody propose an alternative testing methodology? I want to see if the NLPRG has 2^n states where n is the number of registers.

From here on I will call this circuit Non-Linear Pseudo Random Generator NLPRG for simplicity.

Below some circuit typologies ranging from 3 up to 16 bits ( if you somebody wants I can explain how it works and provide the Verilog an C code ).

I tested all the NLPRG sequences with a counter. For example in the 16 bits case, both of them are initialized with 0x0000, any number would work. If the counter or the NLPRG reaches the number 0x0000, than end the simulation. If at the end of the simulation, both the counter and the nlprg are in the 0x0000 state than the sequence of the nlprg is complete.

But this approach does not scale up because the simulation time increases exponentially with the number of bits.

Can somebody propose an alternative testing methodology? I want to see if the NLPRG has 2^n states where n is the number of registers.