arishsu

Member level 3

- Joined

- Sep 10, 2013

- Messages

- 66

- Helped

- 6

- Reputation

- 12

- Reaction score

- 6

- Trophy points

- 8

- Location

- India

- Activity points

- 422

When I simulated my verilog code, the following warning is shown.

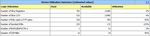

Device utilization summery is as below.

These are my input/output parameters.

How can we reduce the number of bonded IOBs?

Code:

WARNING:Xst:1336 - (*) More than 100% of Device resources are usedThese are my input/output parameters.

Code:

input clk,reset;

input[2:0]prec_sel;

input[5:0]prec_bit;

input[63:0]a,b;

output [63:0]p_d;

output [31:0]p_s;

output reg[24:0]p_16;

output reg[16:0]p_8;

output reg mode_sel_error;

output out_rdy;How can we reduce the number of bonded IOBs?