junsik

Junior Member level 2

I'm reading a paper,

Malobabic, S.; Ellis, D.F.; Salcedo, J.A.; Yuanzhong Zhou; Hajjar, J.-J.; Liou, J.J., "Gate oxide evaluation under very fast transmission line pulse (VFTLP) CDM-type stress," Devices, Circuits and Systems, 2008. ICCDCS 2008. 7th International Caribbean Conference on , vol., no., pp.1,8, 28-30 April 2008

doi: 10.1109/ICCDCS.2008.4542669

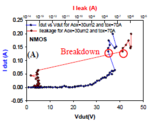

In this paper, the uploaded graph is contained to check the NMOS gate oxide breakdown point by ESD stress.

I have some problem to read the graph. Please tell me the way to read the graph. or some information the graph. what is it called?