melkord

Full Member level 3

I am reading the book by Binkley in order to characterize my device by using Inversion Coefficient method.

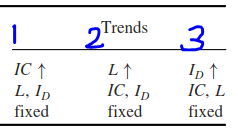

This is from Table 4.1 from the book.

What setup should I used to get IC constant?

The constant IC is used in Trend #2 and #3

I have checked other sources about Inversion Coefficient like, this and this and this, but I am still confuse how to extract the parameters, i.e., what to sweep? what to be fixed?.

Previously, I used gm/Id method.

This is similar with Trend #1 in the picture above.

I sweep VGS. VDS is half VDD. Width is fixed. L is varied for 5 different values.

It works well to extract gm, fT, but not gds.

I need gds information to be able to do the design exploration from the small signal analysis.

If you have any tutorial or other references how to properly setup the circuit to extract those parameter, I would like to know.

This is from Table 4.1 from the book.

What setup should I used to get IC constant?

The constant IC is used in Trend #2 and #3

I have checked other sources about Inversion Coefficient like, this and this and this, but I am still confuse how to extract the parameters, i.e., what to sweep? what to be fixed?.

Previously, I used gm/Id method.

This is similar with Trend #1 in the picture above.

I sweep VGS. VDS is half VDD. Width is fixed. L is varied for 5 different values.

It works well to extract gm, fT, but not gds.

I need gds information to be able to do the design exploration from the small signal analysis.

If you have any tutorial or other references how to properly setup the circuit to extract those parameter, I would like to know.