Syedaaa

Newbie

Hi,

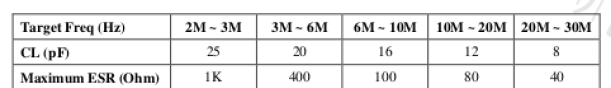

We are using tsmc 28nm PDK. According to the documentation for the oscillator pad "PDXOEDG" we can input max upto 30 MHz with the combination of CL and ESR from the table given in PDK (attach below for reference). In our design we want to have 100 MHz as input frequency without using PLL. Can anyone help that how can we achieve this 100 MHz frequency without using PLL but the Oscillator pad or any other digital/analog IO pad. Also, if we want to use any other pad as an input clock pad rather than oscillator pad of the foundry, how can we estimate that what is the maximum allowable input frequency?

Thanks

Syeda

We are using tsmc 28nm PDK. According to the documentation for the oscillator pad "PDXOEDG" we can input max upto 30 MHz with the combination of CL and ESR from the table given in PDK (attach below for reference). In our design we want to have 100 MHz as input frequency without using PLL. Can anyone help that how can we achieve this 100 MHz frequency without using PLL but the Oscillator pad or any other digital/analog IO pad. Also, if we want to use any other pad as an input clock pad rather than oscillator pad of the foundry, how can we estimate that what is the maximum allowable input frequency?

Thanks

Syeda