bhl777

Full Member level 6

Hi All, I am using the circuit from this paper in designing a PTAT circuit

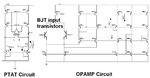

"A Novel Wide-Temperature-Range, 3.9 ppm/C CMOS Bandgap Reference Circuit",by changing the input transistor of opamp from MOSFET to BJT.

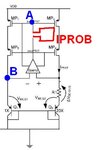

This is the PTAT circuit and the detailed schematic of Opamp. Startup circuit is not included in this figure.

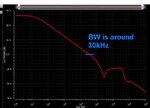

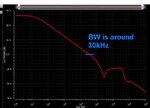

When I did the stability analysis in Cadence, by injecting IPROB at the output node of opamp, I got this bode plot

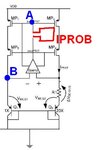

As this figure shows, I tried to put a cap in A node and another one in B node, but they does not help in increasing the BW.

(1) I do not know if my IPROB location is correct or not.The purpose of this BW increment is to deal with high Slew rate VCC raising, eg,1us from 0V to 2.5V.

(2) if it is correct, could anyone tell me where I can try to put the cap or RC to increase the bandwidth?

(3) if the iprobe injection is not correct for the preparation of start up, could anyone show me how to do the frequency compensation? I tried to inject the IPROB in the path of current mirror to negative input side of opamp, but the low frequency gain is 0dB and higher frequency gain is smaller, it seems like that is not a right way to probe the bandwidth of this PTAT circuit.

Thank you!

"A Novel Wide-Temperature-Range, 3.9 ppm/C CMOS Bandgap Reference Circuit",by changing the input transistor of opamp from MOSFET to BJT.

This is the PTAT circuit and the detailed schematic of Opamp. Startup circuit is not included in this figure.

When I did the stability analysis in Cadence, by injecting IPROB at the output node of opamp, I got this bode plot

As this figure shows, I tried to put a cap in A node and another one in B node, but they does not help in increasing the BW.

(1) I do not know if my IPROB location is correct or not.The purpose of this BW increment is to deal with high Slew rate VCC raising, eg,1us from 0V to 2.5V.

(2) if it is correct, could anyone tell me where I can try to put the cap or RC to increase the bandwidth?

(3) if the iprobe injection is not correct for the preparation of start up, could anyone show me how to do the frequency compensation? I tried to inject the IPROB in the path of current mirror to negative input side of opamp, but the low frequency gain is 0dB and higher frequency gain is smaller, it seems like that is not a right way to probe the bandwidth of this PTAT circuit.

Thank you!

Last edited: