timedate

Member level 5

I try to simplify my questions in the last thread , then I realized I failed...

Here is my original question....

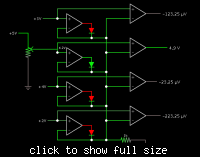

I try to build a photodiode array which contains 4 photodiodes. Each photodiode is connected with its own TIA (transimpedance amplifier), and then connected to LA (Limiting amplifier) through a switch.

I want choose the photodiode which receives largest optical power, turn on the switch, connected with LA. Meanwhile, turn off the other 3 switches.

The TIA I am using has the function that can monitor the current flow through the TIA (pin 'monitor'). So, by comparing this current (actually, it is the voltage) I can know which photodiode tcan receive the largest optical power.

Attached is my schematic, the question is , which is simplest way to achieve the "decision circuit"? could this pure analog? avoid using FPGA? for example using 3 comparators....

*

*

Here is my original question....

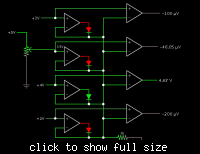

I try to build a photodiode array which contains 4 photodiodes. Each photodiode is connected with its own TIA (transimpedance amplifier), and then connected to LA (Limiting amplifier) through a switch.

I want choose the photodiode which receives largest optical power, turn on the switch, connected with LA. Meanwhile, turn off the other 3 switches.

The TIA I am using has the function that can monitor the current flow through the TIA (pin 'monitor'). So, by comparing this current (actually, it is the voltage) I can know which photodiode tcan receive the largest optical power.

Attached is my schematic, the question is , which is simplest way to achieve the "decision circuit"? could this pure analog? avoid using FPGA? for example using 3 comparators....

*

*