alpeshchokshi

Full Member level 2

- Joined

- Mar 5, 2006

- Messages

- 127

- Helped

- 4

- Reputation

- 8

- Reaction score

- 0

- Trophy points

- 1,296

- Location

- San Jose, CA

- Activity points

- 2,064

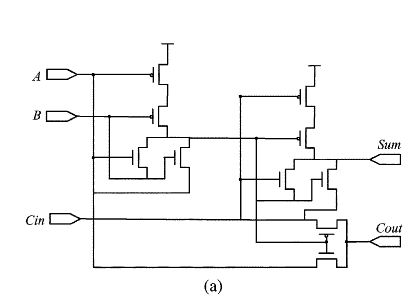

how many min. no. of MOS transistors are required to implement full adder???

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

Hi friend....

Can you explain how this circuit gets the outputs of full adder? Of course, I didn't check all conditions. Suppose I take A=0, B=0 and C=1. Accroding to this inputs we have to get the carry output is 0. But, in this circuit we get, 1.

Even, Why you are using A xor B as input for carry output?