arminb73

Junior Member level 3

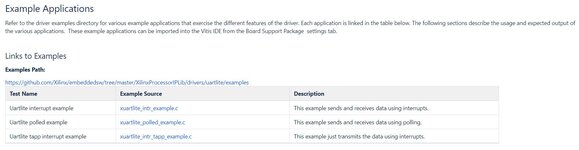

When wanting to experiment with different IPs as an example the AXI UART16550 how is one supposed to design the block design in order to make the Xilinx C examples "correspond" well with the exported block design.

As an example. When wanting to experiment with this C code:

https://github.com/Xilinx/embeddeds.../uartns550/examples/xuartns550_intr_example.c

How am I supposed to do the block design connection in Vivado before exporting the hardware to be used in Vitis?

As an example. When wanting to experiment with this C code:

https://github.com/Xilinx/embeddeds.../uartns550/examples/xuartns550_intr_example.c

How am I supposed to do the block design connection in Vivado before exporting the hardware to be used in Vitis?