rocking_vlsi

Member level 5

How do we define a clock domain? Can 50Mhz and 150Mhz could be synchronous?

Posted via Topify on Android

Posted via Topify on Android

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

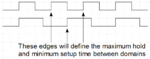

If they were both derived from the same clock source they could be considered synchronous, but because of the difference in frequencies every third rising edge of 100 MHz will line up with every second rising edge of 150 MHz, hence you will have extra clock edges that will reduce the setup time for transfers between the clock domains.

View attachment 102943

regards