Jason_kang

Newbie

Hi,

I am currently designing LC VCO with CMOS process. The frequency of interest is K/Ka band.

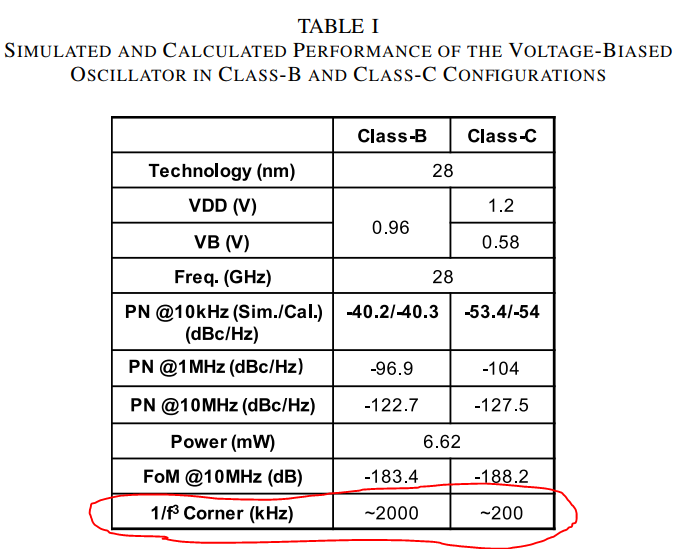

In some of published papers, we can see that the flicker corner frequency is specified.

(source : Y. Hu, T. Siriburanon and R. B. Staszewski, "Intuitive Understanding of Flicker Noise Reduction via Narrowing of Conduction Angle in Voltage-Biased Oscillators," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 66, no. 12, pp. 1962-1966, Dec. 2019, doi: 10.1109/TCSII.2019.2896483. )

The question is, how can I specify the flicker corner frequency in simulation tool(ex. spectre Pnoise)?

If there is no proper way, I should calculate and get the dBc change per octave(dBc/octave), which is considered a very inefficient way.

Thanks.

I am currently designing LC VCO with CMOS process. The frequency of interest is K/Ka band.

In some of published papers, we can see that the flicker corner frequency is specified.

(source : Y. Hu, T. Siriburanon and R. B. Staszewski, "Intuitive Understanding of Flicker Noise Reduction via Narrowing of Conduction Angle in Voltage-Biased Oscillators," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 66, no. 12, pp. 1962-1966, Dec. 2019, doi: 10.1109/TCSII.2019.2896483. )

The question is, how can I specify the flicker corner frequency in simulation tool(ex. spectre Pnoise)?

If there is no proper way, I should calculate and get the dBc change per octave(dBc/octave), which is considered a very inefficient way.

Thanks.