NerdyRocker54

Newbie level 4

I want to implement a sequential circuit using verilog that functions as a 4-bit universal shift register. The shift register will have two inputs that specifies which function the register will perform: 0 0- No change, 0 1-Shift Right, 1 0- Rotate Left, 1 1- Parallel Load

If the shift register is performing a right or left shift it is to get its input from the serial input. Everything is happening at the posedge of the clock.

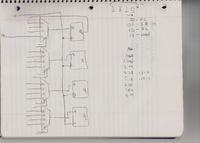

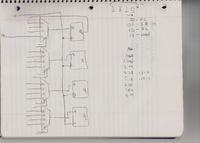

I need help with the the structural implementation that uses 4 4-to-1 muxs and 4 1bit D-ff modules.

So far i have a 4:1 mux, a D-FF, and a "debounce" module, as well as a schematic.

4:1 Mux

module 4to1_mux(data,out,sel);

input [3:0]data;

input [1:0] sel;

output out;

reg out;

always @(data,sel)

begin

case ({data,sel})

2'b00: out = out;

2'b01: out = data[1];

2'b10: out = data[2];

2'b11: out = data[3];

default: out = 2'bXXXX;

endcase

end

endmodule

module dFF(D,Q,clk,rst);

input D,clk,rst;

output Q;

reg Q;

always @ (posedge clk, posedge rst)

begin

if (rst==1'b1)

Q <= D;

else

Q <= Q;

end

endmodule

If the shift register is performing a right or left shift it is to get its input from the serial input. Everything is happening at the posedge of the clock.

I need help with the the structural implementation that uses 4 4-to-1 muxs and 4 1bit D-ff modules.

So far i have a 4:1 mux, a D-FF, and a "debounce" module, as well as a schematic.

4:1 Mux

module 4to1_mux(data,out,sel);

input [3:0]data;

input [1:0] sel;

output out;

reg out;

always @(data,sel)

begin

case ({data,sel})

2'b00: out = out;

2'b01: out = data[1];

2'b10: out = data[2];

2'b11: out = data[3];

default: out = 2'bXXXX;

endcase

end

endmodule

module dFF(D,Q,clk,rst);

input D,clk,rst;

output Q;

reg Q;

always @ (posedge clk, posedge rst)

begin

if (rst==1'b1)

Q <= D;

else

Q <= Q;

end

endmodule