vishnu36

Junior Member level 2

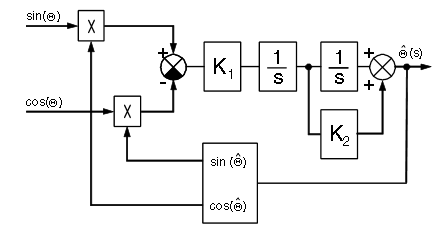

I have task of decoding the position signal from resolver/encoder quadrature outputs. I have used angle tracking observer algorithm method to decode the angle theta in matlab. I want to convert it to fixed point from first principles( not using matlab fixed point advisor) for FPGA implementation. The algorithm requirement is shown below:

The range of sine/cosine theta is 0-5Vpp. How should I decide the fixed point sizing of the above elements and successfully implement it in FPGA. I had used AN3943 for my understanding of the algorithm.

The range of sine/cosine theta is 0-5Vpp. How should I decide the fixed point sizing of the above elements and successfully implement it in FPGA. I had used AN3943 for my understanding of the algorithm.