explorick

Advanced Member level 4

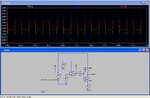

There is a variable voltage coming as Vin which can be vary between 3.3 and 1.1V. For Vin voltages between 3.3 to 2.1V the output should be 3.3 to 2.1V, for voltage less than 2.1V the output should be fixed at 2.5V. For this i created a circuit and was not successful with it because the body diode of PMOS is conducting when control voltage is high. Is there any other circuit you could suggest. I cannot use diode in the Vout path as that would add drop. The circuit an observation is as attached.