kokei74

Junior Member level 3

Hello Guys

I need a help with full operational in VHDL that can execute this matrix multiplier.

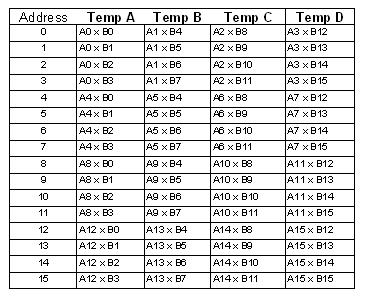

This is a 4x4 matrix multiplier i try to make. It has 3-level of step which is :

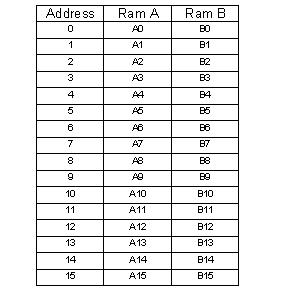

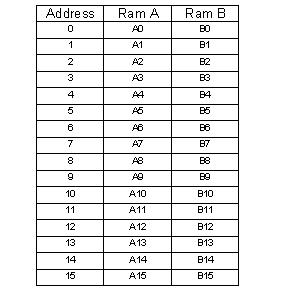

1st lvl - data write in Ram A and Ram B

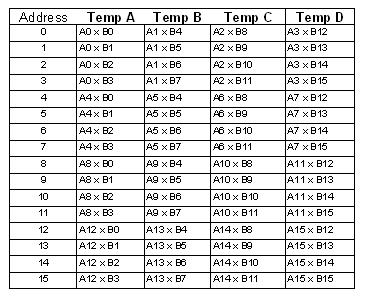

2nd lvl - result from multiplication will be stored in temp A,B,C,D

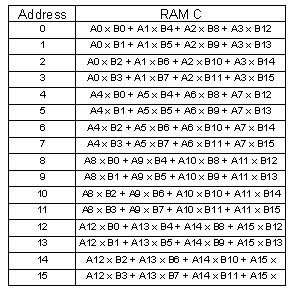

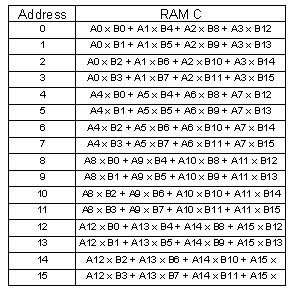

3rd lvl - result from multiplication in temp A,B,C,D will be added together to form 1 element in resulted matrix.

This is hardware implementation of this matrix multiplier.

I need a help with full operational in VHDL that can execute this matrix multiplier.

This is a 4x4 matrix multiplier i try to make. It has 3-level of step which is :

1st lvl - data write in Ram A and Ram B

2nd lvl - result from multiplication will be stored in temp A,B,C,D

3rd lvl - result from multiplication in temp A,B,C,D will be added together to form 1 element in resulted matrix.

This is hardware implementation of this matrix multiplier.