anotherbrick

Full Member level 4

- Joined

- Jan 10, 2009

- Messages

- 217

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,298

- Location

- Istanbul , Turkey

- Activity points

- 3,142

hello dear Forum,

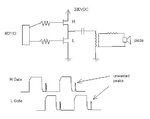

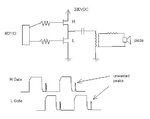

I have designed a 1 KW ultrasonic generator with an half bridge for 28 KHz frequency

however I am facing a problem with false turning ON of IRFP460 mosfets

the H mosfet is driven ON (unwanted peak) when the L mosfet is driven ON (wanted) by IR2113

and vice versa

I have scetched the circuit and mosfet gate signals at attached drawing

what is your advice how can eliminate the unwanted gate signals

thank you

I have designed a 1 KW ultrasonic generator with an half bridge for 28 KHz frequency

however I am facing a problem with false turning ON of IRFP460 mosfets

the H mosfet is driven ON (unwanted peak) when the L mosfet is driven ON (wanted) by IR2113

and vice versa

I have scetched the circuit and mosfet gate signals at attached drawing

what is your advice how can eliminate the unwanted gate signals

thank you