gatedriver

Junior Member level 1

Hi everyone,

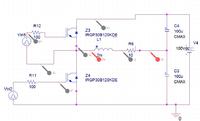

I am doing simulation gate driver by Orcad - pspice. But i met so many problem with this device.

- gate driver model: IR2106 (downloaded from IR website)

- PWM input are square waves (1kHz) from 0-3.3V

- It also included delay time 0.4us for dead time

- the type of diode is fast reverse recovery

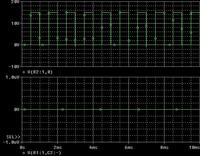

When I simulated this gate drive sepearate, The ouput signals on HO, LO pins are ok.

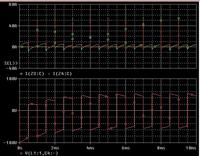

But when I applied power circuit (half bridge), the convergence problem always happen.

The problem report usually mention the errors relate to some diodes of of IR2106 and switches.

My silmulation settling:

TSTOP 2.5ms

Maximum step 0.1u (some time I increase to 12u, but the same result)

RELTOL 0.1; VNTOL 0.1; ABSTOL 1u; CHGTOL 0.01N; ITL4 150; ITL1 500;

I do this simulation during two weeks, but the result is always convergence problem.

Could anyone please help me to solve this problem?

Thank you very much!

I am doing simulation gate driver by Orcad - pspice. But i met so many problem with this device.

- gate driver model: IR2106 (downloaded from IR website)

- PWM input are square waves (1kHz) from 0-3.3V

- It also included delay time 0.4us for dead time

- the type of diode is fast reverse recovery

When I simulated this gate drive sepearate, The ouput signals on HO, LO pins are ok.

But when I applied power circuit (half bridge), the convergence problem always happen.

The problem report usually mention the errors relate to some diodes of of IR2106 and switches.

My silmulation settling:

TSTOP 2.5ms

Maximum step 0.1u (some time I increase to 12u, but the same result)

RELTOL 0.1; VNTOL 0.1; ABSTOL 1u; CHGTOL 0.01N; ITL4 150; ITL1 500;

I do this simulation during two weeks, but the result is always convergence problem.

Could anyone please help me to solve this problem?

Thank you very much!

Attachments

Last edited: