perado

Full Member level 2

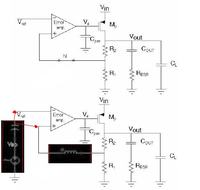

why we should draw frequency response for open-loop circuit in LDO that uses feedback?

Isnt true that draw this for feedback circuit?

what I should do to draw frequency response of a LDO circuit?

Isnt true that draw this for feedback circuit?

what I should do to draw frequency response of a LDO circuit?