Rodney123

Newbie

Hi All,

I am attempting to program MPF300T-1FCG784I device using Libero v12.6 (Platnium) with FlashPro 4 programmer (JTAG). However I get the following error when programming.

Error: programmer '01416' : device 'MPF300(T|TS|TL|TLS)' : Executing action PROGRAM FAILED, EXIT -22, refer to FlashPro online help for details.

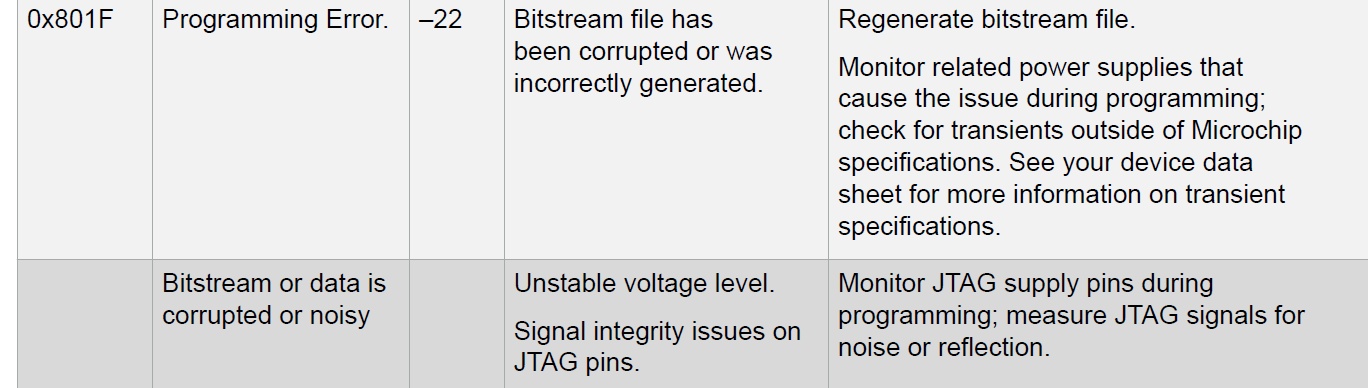

More information this error

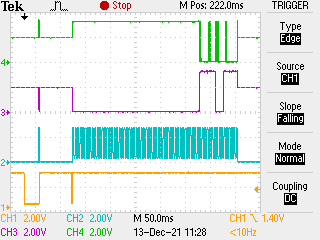

To deal with this issue I have taken a closer look at my JTAG signals to see is signal integrity could be an issue.

Green: TMS

Purple: TDI

Blue: CLK

Orange: TRST

To achieve this JTAG "frame" I ran a "Scan and Check Chain" operation.

So my questions are as follows:

Do the above JTAG signals look acceptable?

I have noticed that both TMS and TDI seem to float until the CLK kicks in

Should reset be high during the transmission of the frame?

I believe the JTAG State machine to be active whilst TRST is low. am i pumping data in to a SM that is in reset.

Is their a resource that describes JTAG framing and protocol?

most of my questions stem from a weak understanding of what JTAG signals should look like (framing and protocol).

What exactly does the "scan and check chain" do?

At a guess I would say checks the programmer is connected and that it can clock data into and out of the target device/s Instruction register/s as expected.

I am attempting to program MPF300T-1FCG784I device using Libero v12.6 (Platnium) with FlashPro 4 programmer (JTAG). However I get the following error when programming.

Error: programmer '01416' : device 'MPF300(T|TS|TL|TLS)' : Executing action PROGRAM FAILED, EXIT -22, refer to FlashPro online help for details.

More information this error

To deal with this issue I have taken a closer look at my JTAG signals to see is signal integrity could be an issue.

Green: TMS

Purple: TDI

Blue: CLK

Orange: TRST

To achieve this JTAG "frame" I ran a "Scan and Check Chain" operation.

So my questions are as follows:

Do the above JTAG signals look acceptable?

I have noticed that both TMS and TDI seem to float until the CLK kicks in

Should reset be high during the transmission of the frame?

I believe the JTAG State machine to be active whilst TRST is low. am i pumping data in to a SM that is in reset.

Is their a resource that describes JTAG framing and protocol?

most of my questions stem from a weak understanding of what JTAG signals should look like (framing and protocol).

What exactly does the "scan and check chain" do?

At a guess I would say checks the programmer is connected and that it can clock data into and out of the target device/s Instruction register/s as expected.

Last edited: