yefj

Advanced Member level 4

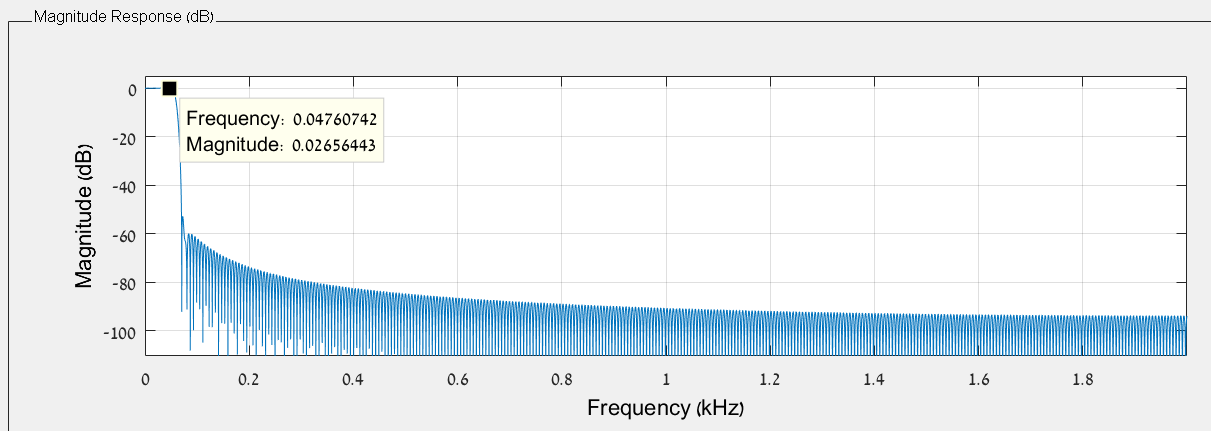

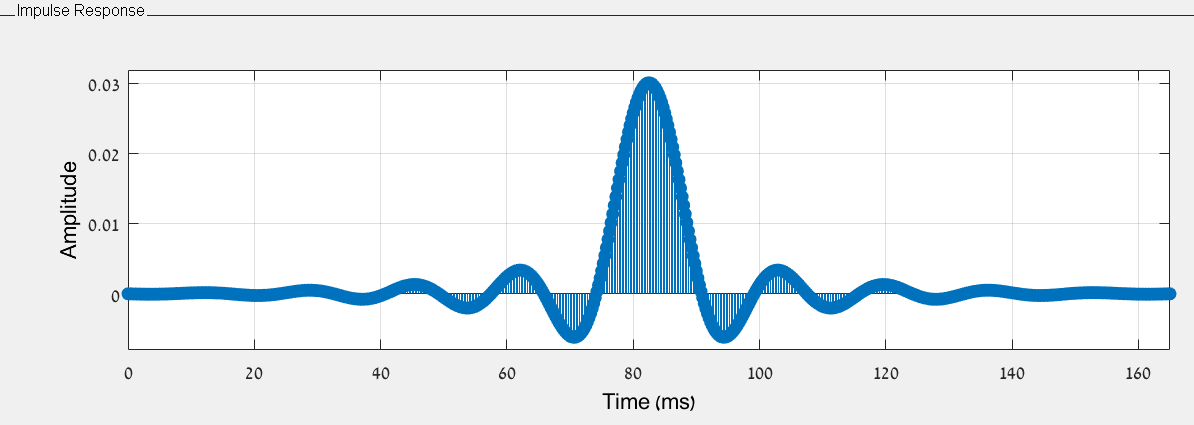

Hello, I have used matlab to create a filter with response as shown bellow.

using matlab i created the attached file with the coefficients

csvwrite('FilterCoef.txt',Num)

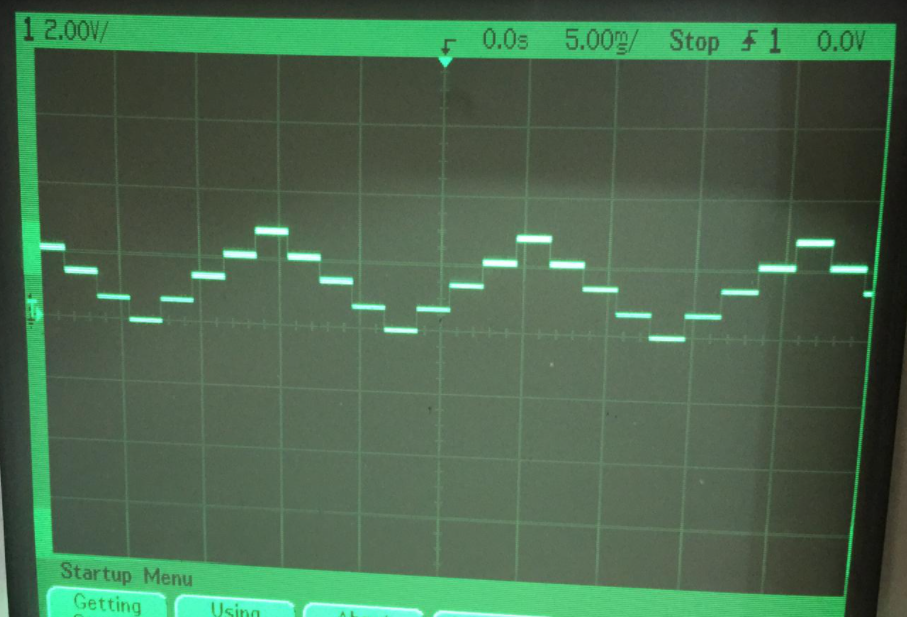

i have created a stepped response as shown bellow,after that i am olanning to connect the DAC output to ADC input.

then i have an array of a samples and i do a convolution between the sampled array and the filter array.

two question are rising afterwards:

how many ADC samples do i need for the convoltion to do correct filterring?

How then i present the filtered data?(sending it again to DAC?)

Thanks.

using matlab i created the attached file with the coefficients

csvwrite('FilterCoef.txt',Num)

i have created a stepped response as shown bellow,after that i am olanning to connect the DAC output to ADC input.

then i have an array of a samples and i do a convolution between the sampled array and the filter array.

two question are rising afterwards:

how many ADC samples do i need for the convoltion to do correct filterring?

How then i present the filtered data?(sending it again to DAC?)

Thanks.