Annee

Newbie

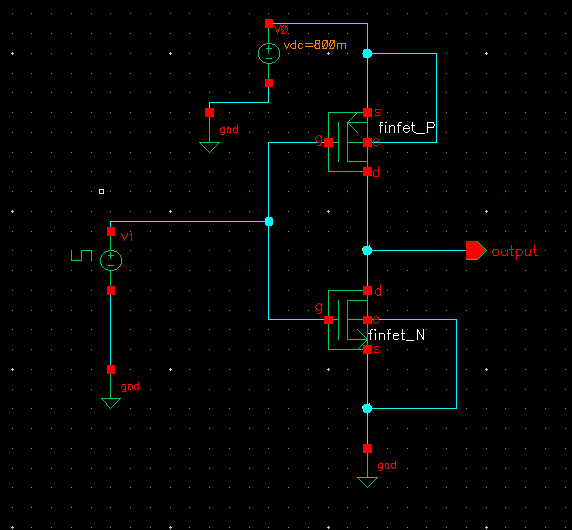

We have been designing a finfet_32nm invertor in cadence as part of our research. However we are not getting the desired output

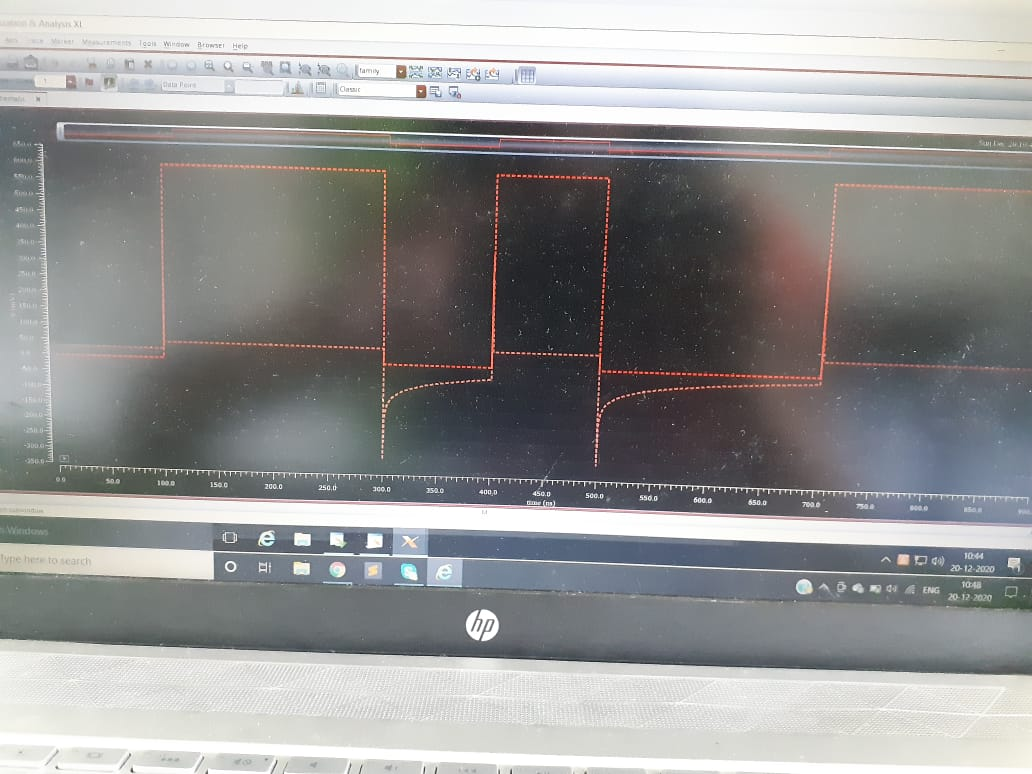

this is the invertor we designed. the out put we got is

we have currently given Vds values as 1V,0.6V,0.8V but none of these values also worked. Kindly suggest me wether there is an error in the design or the values we have provided

Thank you

this is the invertor we designed. the out put we got is

we have currently given Vds values as 1V,0.6V,0.8V but none of these values also worked. Kindly suggest me wether there is an error in the design or the values we have provided

Thank you