eslavko

Junior Member level 2

- Joined

- Jan 22, 2010

- Messages

- 22

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Location

- Slovenia, EU.

- Activity points

- 1,479

Hello....

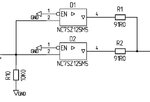

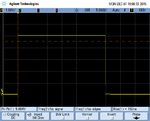

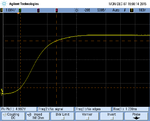

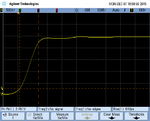

Long time ago I build TDR. It has 47AC14 as pulse generator, but now I want to improve it. AC14 is just little to slow and has excsive ringing. I do search a lot and found that SRD is way to go. (Avalanche generator is other direction as I want step and not pulse) HC14 has no ringing but is slower too.

So SRD diode is not easy to get, and seems expensive to. Then I found one paper at https://www.adv-radio-sci.net/2/7/2004/ars-2-7-2004.pdf

that use BJT instead SRD for same functionality. But sadly there are no schematic how to connect transistor and I don't find solution yet. Basically I ned to put transistor into saturation and then reverse bias it. How to do with one signal?!?

Thanks

Long time ago I build TDR. It has 47AC14 as pulse generator, but now I want to improve it. AC14 is just little to slow and has excsive ringing. I do search a lot and found that SRD is way to go. (Avalanche generator is other direction as I want step and not pulse) HC14 has no ringing but is slower too.

So SRD diode is not easy to get, and seems expensive to. Then I found one paper at https://www.adv-radio-sci.net/2/7/2004/ars-2-7-2004.pdf

that use BJT instead SRD for same functionality. But sadly there are no schematic how to connect transistor and I don't find solution yet. Basically I ned to put transistor into saturation and then reverse bias it. How to do with one signal?!?

Thanks