ee_wmxaa

Newbie level 6

assura label short problem

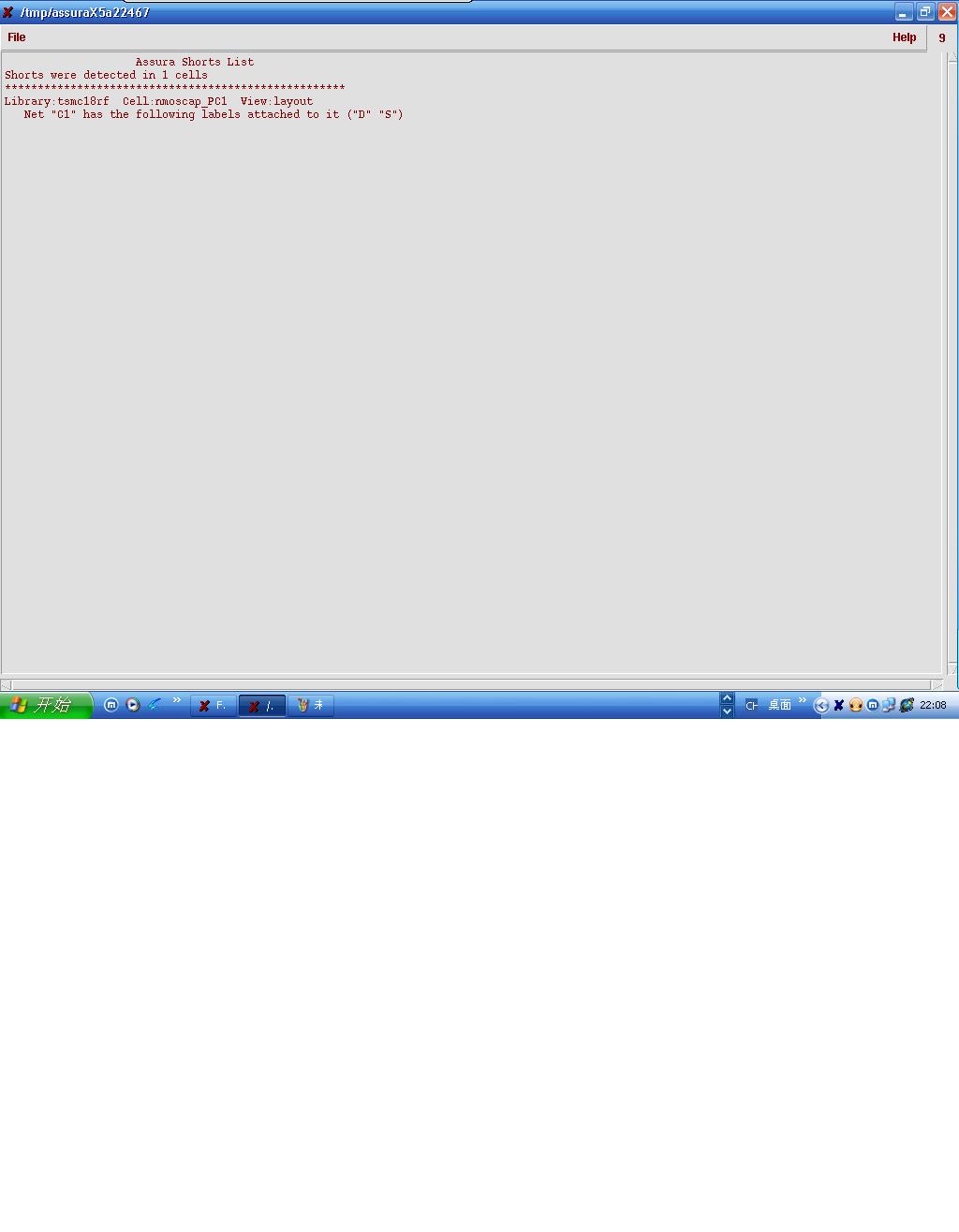

Hi, everyone. I was doing LVS check recently, I found my schematic and layout matched in the "compare" window, but in the "extract" window (also in the LVS result window), I found a short problem. In the summary file, it said "1 cells has 1 label short problems". I do not know how to deal with it. What is "label short"??? I wonder whether anyone can help me with this problem. Many thanks

Hi, everyone. I was doing LVS check recently, I found my schematic and layout matched in the "compare" window, but in the "extract" window (also in the LVS result window), I found a short problem. In the summary file, it said "1 cells has 1 label short problems". I do not know how to deal with it. What is "label short"??? I wonder whether anyone can help me with this problem. Many thanks