EEcrazy

Newbie

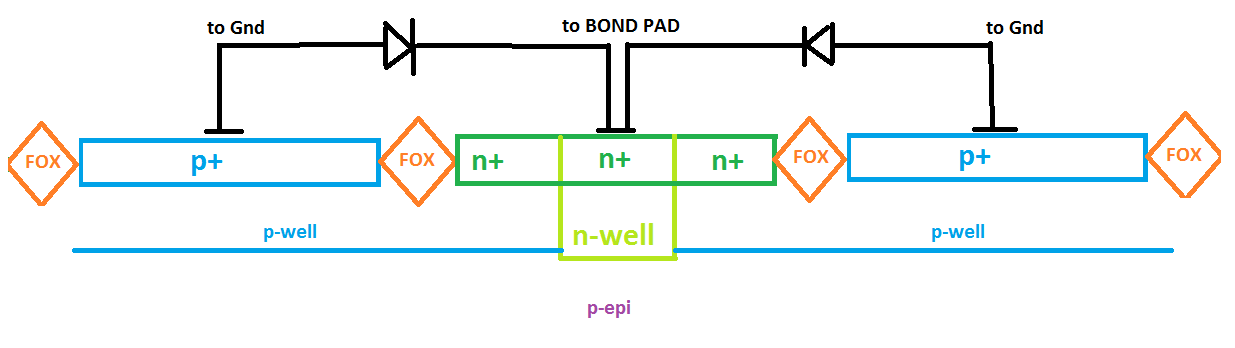

Does this layout for finger ESD protection diode make any sense? What is the reason for adding n-well right under the n+ contacts?

Or may be I have p&n backwards, so its actually SCR?

Thx!

Or may be I have p&n backwards, so its actually SCR?

Thx!