allennlowaton

Full Member level 5

good day guys..

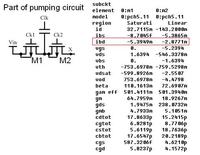

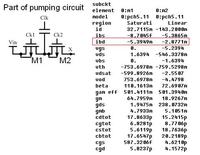

I am doing charge pump for white LED now.

The output current is around 60mA (for the three white LEDs in parallel)

I checked the two power PMOS, and I found out that there's a 5 to 10mA current

that flows from drain to bulk (Ibd).

How can avoid this? or is there any technique to minimize it?

[/url]

[/url]

Thank you..

I am doing charge pump for white LED now.

The output current is around 60mA (for the three white LEDs in parallel)

I checked the two power PMOS, and I found out that there's a 5 to 10mA current

that flows from drain to bulk (Ibd).

How can avoid this? or is there any technique to minimize it?

Thank you..