kishore680

Member level 5

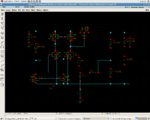

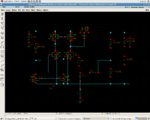

Hello all i want to find out gain and phase margin of an LDO.So in order to that i have done ac analysis by breaking the loop and placing inductor and Coupling ac to the + terminal as shown here

. Is this the right way is my first question

. Is this the right way is my first question

second question.Where the phase angle should start -180 or 180. Cause i plotted from 1 hz to 1Ghz and 100 hz to 1G hz in cadence. I got two different results as shown below.

why is that so? . Which is correct and why? ac magnitude=1mv

. Is this the right way is my first question

. Is this the right way is my first questionsecond question.Where the phase angle should start -180 or 180. Cause i plotted from 1 hz to 1Ghz and 100 hz to 1G hz in cadence. I got two different results as shown below.

why is that so? . Which is correct and why? ac magnitude=1mv

Last edited: