ffsher100

Junior Member level 3

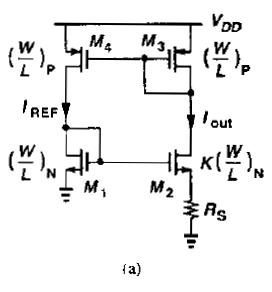

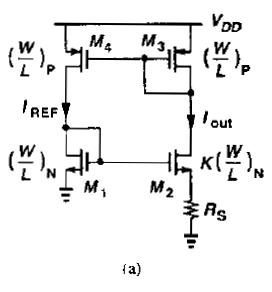

i got a question from Razavi textbook in chapter 11.2 : Supply-Independent Biasing

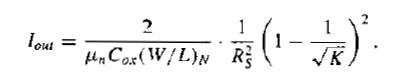

===><figure 1>

===><figure 1>

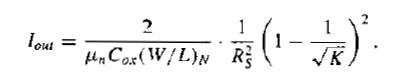

===><figure 2>

===><figure 2>

by figure2, it looks like vdd really has no effect on the figure 1 CKT.

the textbook also introduce start-up circuit M5 into the design as following:

===><figure 3>

===><figure 3>

when simulating the circuit with startup(M5), it seem to be effected by VDD.

Current Iout, Iref vary with VDD.

In practice, figure 3 become Supply-dependent Biasing since startup must include.

how could this be? if using figure 3, supply- independent case never happen.

below figure, i sweep .dc vdd.

As you see vdd ramp from 0v to 5v, current Iref and Iout are not constant if vdd>2.8v

by figure2, it looks like vdd really has no effect on the figure 1 CKT.

the textbook also introduce start-up circuit M5 into the design as following:

when simulating the circuit with startup(M5), it seem to be effected by VDD.

Current Iout, Iref vary with VDD.

In practice, figure 3 become Supply-dependent Biasing since startup must include.

how could this be? if using figure 3, supply- independent case never happen.

below figure, i sweep .dc vdd.

As you see vdd ramp from 0v to 5v, current Iref and Iout are not constant if vdd>2.8v

Last edited: