melkord

Full Member level 3

I have been reading about random mismatch from some sources like here, here, here, and ch4 of this book.

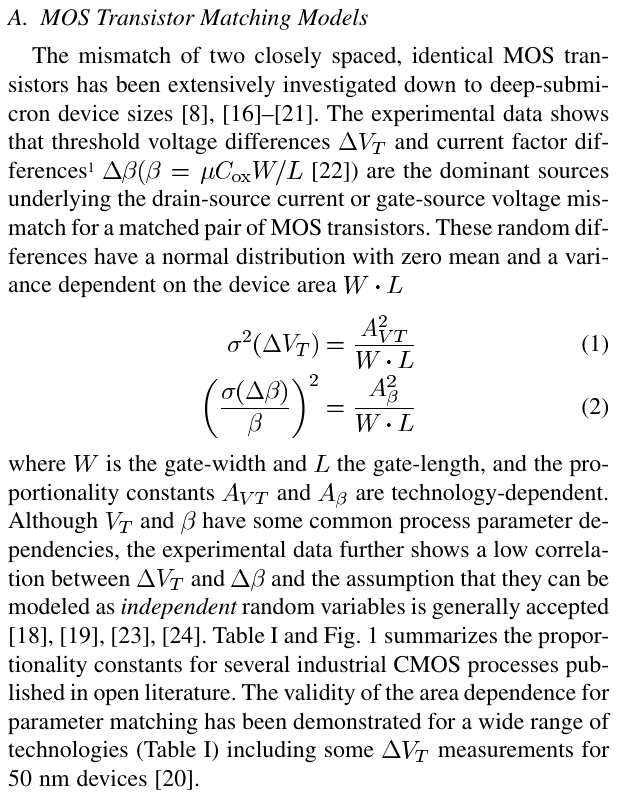

From what I read, I found that on device level, the matching only depends on W, L, and technology. See picture below.

So, should we characterize our technology regarding mismatch? if yes, How?

I am still checking it, but it seems that A_VT is not constant in my technology. I might be incorrect about this though.

From what I read, I found that on device level, the matching only depends on W, L, and technology. See picture below.

So, should we characterize our technology regarding mismatch? if yes, How?

I am still checking it, but it seems that A_VT is not constant in my technology. I might be incorrect about this though.