cgchas

Member level 3

- Joined

- Jul 19, 2011

- Messages

- 56

- Helped

- 2

- Reputation

- 8

- Reaction score

- 4

- Trophy points

- 1,288

- Activity points

- 2,001

I am designing a wide band amplifier (20Hz to 50MHz) that follows a frequency compensated attenuator network. This amplifier will provide signal to a frequency counter that I have built.

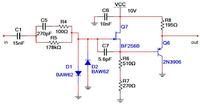

The amplifier is expected function with signals as small as 15mVpp - 50mVpp input, but for breadboard testing, I have been bypassing the attenuator and just using a small protection network (270p cap in series with 100 ohm resistor both in parallel to 178k resistor followed by a diode AC clamp). A 3.3 volt 50MHz input comes through the diodes at about just under 500mVpp.

The first amplification stage is a buffer/impedance converter, common drain BF256B N-Channel JFET direct coupled to a common collector 2N3906 PNP BJT . This transforms impedance from high (>1Mohm) down to about 150 ohms and then from 150 down to 50 (I think). The voltage out of this buffer is about 1Vpp and if I load test it with a 50-ohm resistor it drops to 500mVpp.

From there I have tried quite a few different things. What I want to do, is from a +10V single supply amplify 15mVpp up high enough so that the final current buffer stage can drive a 5V 50-ohm load to 74F Schottky NAND gates. This output voltage does not technically need to be 5 volts. It can be lower as far as the NAND gates are concerned (they technically work at 2V input), but I would like to know how to get as close to 10 as possible from a 10 volt rail. I am not opposed to line drivers but I still want to know how to make this signal with transistors if it is possible. I am not opposed to resorting to a higher supply rail if it is absolutely necessary, but so far I do not know if it is.

Here is what I have tried so far..

BC547C common emitter capacitively coupled to 2N3904 common collector. From just this pair I can get from 1V to 2.5-2.75Vpp. With 2 additional stages I can only get to about 4.5Vpp. I cannot seem to get around the loading effects of each stage using the basic CE / CC combination regardless of how I bias them.

If I bootstrap the follower buffers instead of the basic emitter followers this definitely lowers output impedance, but my lack of experience with these is making it difficult to bias them for proper output impedance. All of my tests have shown their output resistances to be <3-4 ohms, but I have to admit, they do seem to buffer very well. With a single BC547C and 2N3904 I can get to just over 4.5Vpp but not at 50-ohms output. I have not yet been able to mathematically process the AC equivalent model of the bootstrap (positive feedback) follower yet and I would like to correctly get to 50 ohms. I'd love some guidance with this, but only if this is the recommended way to solve my problem.

I have tried 4 capacitively coupled stages of BC547C common emitters followed by a single 2N3904 buffer. The best I have been able to get from this is just over 4Vpp.

I have also tried a OPA830 Op-Amp. I have tried it right after the first N-JFET/PNP stage as well as I have tried it after one or more stages of the BC547C/2N3904 combinations. The best I have been able to come up with (with reasonable stability) is 5.5 - 6Vpp. (7-8 volts with jitter and some instability). I am not opposed to using 1 or more op amps in my final design but I would very much like to know how to do this with basic discrete models.

Here are the top 2 questions I have after experimenting for the past 3 weeks with this project. I have more but this post is already getting lengthy

1) Is an arrangement of reasonably basic discrete amplifier models, one or more stages, that gets voltage up to 8-9 volts from a 10 volt rail possible to 50MHz?

By basic, I mean voltage divider biased BJT and self-biased JFET or directly coupled common emitter (or source) with emitter or (source) followers.

2) For a multiple stage high frequency small signal amplifier, do I need to be matching output to input impedance at each stage or should I be just worried about not loading subsequent stages by making input impedances as high as possible? In other words, are signal reflections an issue at these levels?

My main criteria here is getting as close to 10V from 15mV as possible and the best I achieved so far is 6V from 500mV and that is without going through the attenuator, so there is plenty of room for improvement.

Any comments or suggestions are appreciated.

The amplifier is expected function with signals as small as 15mVpp - 50mVpp input, but for breadboard testing, I have been bypassing the attenuator and just using a small protection network (270p cap in series with 100 ohm resistor both in parallel to 178k resistor followed by a diode AC clamp). A 3.3 volt 50MHz input comes through the diodes at about just under 500mVpp.

The first amplification stage is a buffer/impedance converter, common drain BF256B N-Channel JFET direct coupled to a common collector 2N3906 PNP BJT . This transforms impedance from high (>1Mohm) down to about 150 ohms and then from 150 down to 50 (I think). The voltage out of this buffer is about 1Vpp and if I load test it with a 50-ohm resistor it drops to 500mVpp.

From there I have tried quite a few different things. What I want to do, is from a +10V single supply amplify 15mVpp up high enough so that the final current buffer stage can drive a 5V 50-ohm load to 74F Schottky NAND gates. This output voltage does not technically need to be 5 volts. It can be lower as far as the NAND gates are concerned (they technically work at 2V input), but I would like to know how to get as close to 10 as possible from a 10 volt rail. I am not opposed to line drivers but I still want to know how to make this signal with transistors if it is possible. I am not opposed to resorting to a higher supply rail if it is absolutely necessary, but so far I do not know if it is.

Here is what I have tried so far..

BC547C common emitter capacitively coupled to 2N3904 common collector. From just this pair I can get from 1V to 2.5-2.75Vpp. With 2 additional stages I can only get to about 4.5Vpp. I cannot seem to get around the loading effects of each stage using the basic CE / CC combination regardless of how I bias them.

If I bootstrap the follower buffers instead of the basic emitter followers this definitely lowers output impedance, but my lack of experience with these is making it difficult to bias them for proper output impedance. All of my tests have shown their output resistances to be <3-4 ohms, but I have to admit, they do seem to buffer very well. With a single BC547C and 2N3904 I can get to just over 4.5Vpp but not at 50-ohms output. I have not yet been able to mathematically process the AC equivalent model of the bootstrap (positive feedback) follower yet and I would like to correctly get to 50 ohms. I'd love some guidance with this, but only if this is the recommended way to solve my problem.

I have tried 4 capacitively coupled stages of BC547C common emitters followed by a single 2N3904 buffer. The best I have been able to get from this is just over 4Vpp.

I have also tried a OPA830 Op-Amp. I have tried it right after the first N-JFET/PNP stage as well as I have tried it after one or more stages of the BC547C/2N3904 combinations. The best I have been able to come up with (with reasonable stability) is 5.5 - 6Vpp. (7-8 volts with jitter and some instability). I am not opposed to using 1 or more op amps in my final design but I would very much like to know how to do this with basic discrete models.

Here are the top 2 questions I have after experimenting for the past 3 weeks with this project. I have more but this post is already getting lengthy

1) Is an arrangement of reasonably basic discrete amplifier models, one or more stages, that gets voltage up to 8-9 volts from a 10 volt rail possible to 50MHz?

By basic, I mean voltage divider biased BJT and self-biased JFET or directly coupled common emitter (or source) with emitter or (source) followers.

2) For a multiple stage high frequency small signal amplifier, do I need to be matching output to input impedance at each stage or should I be just worried about not loading subsequent stages by making input impedances as high as possible? In other words, are signal reflections an issue at these levels?

My main criteria here is getting as close to 10V from 15mV as possible and the best I achieved so far is 6V from 500mV and that is without going through the attenuator, so there is plenty of room for improvement.

Any comments or suggestions are appreciated.