AlienCircuits

Member level 5

Hello,

After careful review of my book Sedra and Smith, I see that in almost all of his designs he references the process parameters K = k'n*(W/L) which has units of mA/V^2.

My problem now (as it was when I first studied it) is that there is a disconnect between what this book teaches and what a MOSFET datasheet provides. I'm hoping someone can clarify this for me.

My MOSFET datasheet only gives me a transconductance parameter g_fs, however this is in units of A/V, so I know that I cannot use the equations Sedra and Smith use with this parameter. I want to use these equations to determine my bias current for saturation operation, iD = K*(Vgs-Vth)^2.

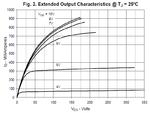

I have asked this question before a long time ago and I never got an answer that actually helped me resolve this issue to where I could start designing FETs as amplifiers with real parts. Without knowing more, the only way I can guess to figure out K would be to try and derive it graphically from the Id - Vds plot of various Vgs curves.

After careful review of my book Sedra and Smith, I see that in almost all of his designs he references the process parameters K = k'n*(W/L) which has units of mA/V^2.

My problem now (as it was when I first studied it) is that there is a disconnect between what this book teaches and what a MOSFET datasheet provides. I'm hoping someone can clarify this for me.

My MOSFET datasheet only gives me a transconductance parameter g_fs, however this is in units of A/V, so I know that I cannot use the equations Sedra and Smith use with this parameter. I want to use these equations to determine my bias current for saturation operation, iD = K*(Vgs-Vth)^2.

I have asked this question before a long time ago and I never got an answer that actually helped me resolve this issue to where I could start designing FETs as amplifiers with real parts. Without knowing more, the only way I can guess to figure out K would be to try and derive it graphically from the Id - Vds plot of various Vgs curves.