maulik_suthar

Junior Member level 1

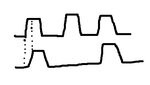

i want the circuit and a proper method to Design a black box whose input clock and output relationship as shown in diagram.

__ __ __ __ __ __ __ __ __

__| |__| |__| |__| |__| |__| |__| |__| |__| |__ <<<<<<< clock

__ __ __ __ __

__| |_ _____| |______| |______ | |______| |__ <<<<<<< Output

__ __ __ __ __ __ __ __ __

__| |__| |__| |__| |__| |__| |__| |__| |__| |__ <<<<<<< clock

__ __ __ __ __

__| |_ _____| |______| |______ | |______| |__ <<<<<<< Output