stenzer

Advanced Member level 3

Hi,

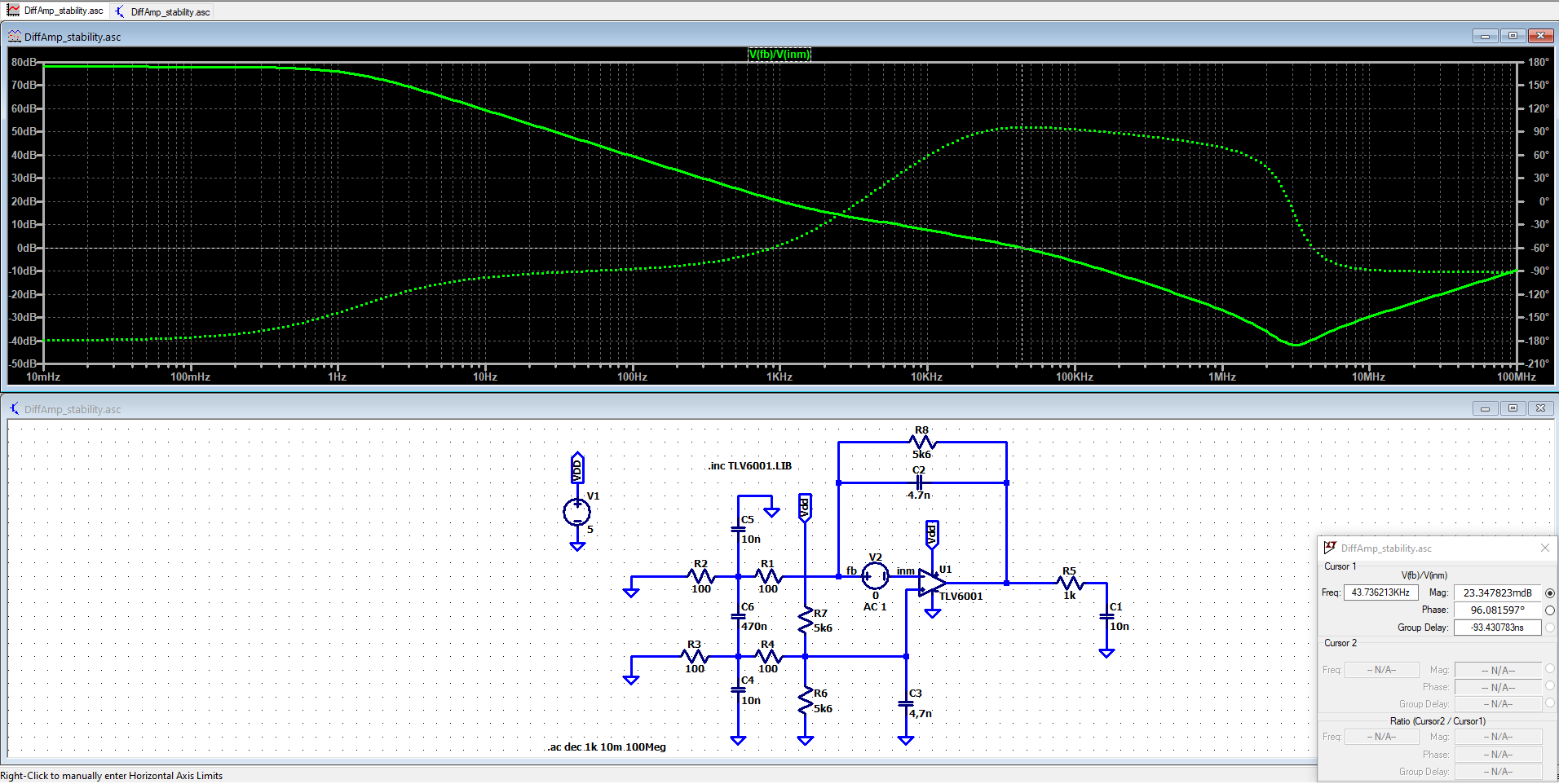

I'm simulated a differential amplifier which also includes a differential and a common mode input filter. I performed a stability analysis in LTSpice according to [1]. As can be seen, the corresponding phase of the the open loop response (loop gain) starts at -180°, and has a phase margin of 96° when the magnidude crosses the 0 dB line.

To consider the circuitry as stable the phase should not be equal -180° for a magnitude of 1 (0 dB) (denominator of the transfere should not be zero ), to be more specific a certain phase margin should be maintained.

), to be more specific a certain phase margin should be maintained.

As the shown circuitry has a phase margin of 96° (@ 0dB) it should be stable. I have performed a couple of stability analysIs in LTSpice so far, but (I think) non started with a phase of -180°. So I wanted to get a feedback from you if my thoughts are correct. Based on my thoughts above, it is only important to have a "large" phase marging (common textbook value is 45°) at a magintude of 0 dB, and to have a small magnitude (<< 0 dB) at -180°.

BR and thank you for your feedback.

[1] https://www.analog.com/en/education/education-library/videos/5579254320001.html

I'm simulated a differential amplifier which also includes a differential and a common mode input filter. I performed a stability analysis in LTSpice according to [1]. As can be seen, the corresponding phase of the the open loop response (loop gain) starts at -180°, and has a phase margin of 96° when the magnidude crosses the 0 dB line.

To consider the circuitry as stable the phase should not be equal -180° for a magnitude of 1 (0 dB) (denominator of the transfere should not be zero

As the shown circuitry has a phase margin of 96° (@ 0dB) it should be stable. I have performed a couple of stability analysIs in LTSpice so far, but (I think) non started with a phase of -180°. So I wanted to get a feedback from you if my thoughts are correct. Based on my thoughts above, it is only important to have a "large" phase marging (common textbook value is 45°) at a magintude of 0 dB, and to have a small magnitude (<< 0 dB) at -180°.

BR and thank you for your feedback.

[1] https://www.analog.com/en/education/education-library/videos/5579254320001.html