the moon is back

Member level 2

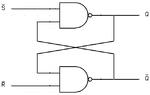

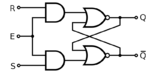

hi, guy s pls explain me how does a flipflop is different from latch?

thank u

thank u

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

hi, guy s pls explain me how does a flipflop is different from latch?

thank u

always @*

if (my_input == 1)

my_output = 0;always @*

case (my_input)

1: my_output = 0;

endcasealways @*

if (my_input == 1)

my_output = 0;

else

my_output = 1;always @*

case (my_input)

1: my_output = 0;

default: my_output = 1;

endcaseassign my_output = ~my_input;

jwdonal, async. latch means latch which doesn't have clk signal and operates only on change in inputs, isn't it?