FlyingDutch

Advanced Member level 1

- Joined

- Dec 16, 2017

- Messages

- 457

- Helped

- 45

- Reputation

- 92

- Reaction score

- 55

- Trophy points

- 28

- Location

- Bydgoszcz - Poland

- Activity points

- 4,954

Hello forum,

I designed a simple development board with FPGA from GowinSemi - IC model: GW1N-LV9LQ144C6/I5. Here is link to mouser.com with this product:

https://www.mouser.com/ProductDetai...W1N-LV9LQ144C6-I5?qs=wnTfsH77Xs6N/yGezJZrJQ==

www.gowinsemi.com

www.gowinsemi.com

Tis is basic FPGA with 8640 LUT and 120 I/Os in LQFP-144 case. The amount of resources allow conduct experiments with Soft-CPU (for example with RISC-V soft-cores). My main goal was to design FPGA development which is cheap, but is suitable for beginners. Apart the FPGA itself the board is equipped with:

1) 24 MHz clock circuit

2) LDO voltage controllers and switches for configuring FPGA I/O Banks (three voltages: 3.3V , 2.5V and 1.2 V

3) FPGA Mode switches (for boot mode)

4) Setup circuitry (Reconfig, Done etc.)

5) FPGA reset circuit

6) USB to JTAG based on FTDI chip FT 2232HL (allowing programing by USB socket)

7) JTAG Header for alternating programming by "Gowin Cable" external programmer

8) Additional 32Mb SPI flash IC

9) 8MB of PSRAM (Pseudo RAM) alowing big frame-buffers

10) DSub15 VGA connector

11) 8 user LEDs

12) 8 DIP-Switches

13) 5 Push Buttons

14) TF (uSD) card module

15) Simple audio output

16) 59 I/O pins led out to the three goldpin connectors

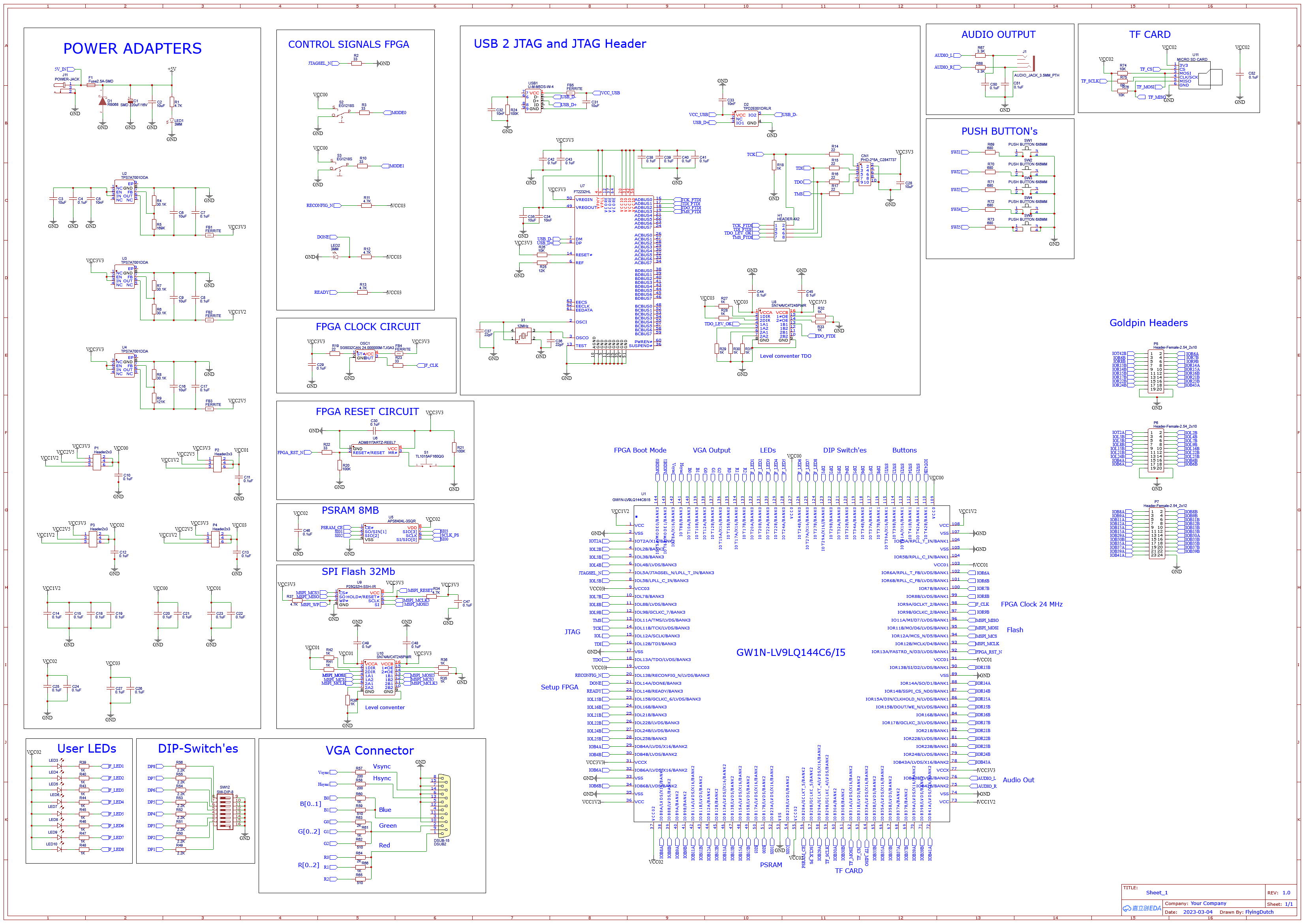

I wanted the FPGA kit had the opportunity to program by USB socket and did not require expensive external programer (Gowin "USB Cable"), hence the use of the FTDI chip . I also wanted the FPGA board bring out a large number of I/O pins. I don't plan to output differential pins (LVDS) with impedance and length control on PCB. Here is finished schematic:

It remains to design the PCB.

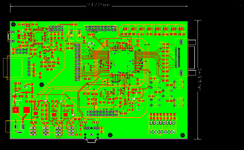

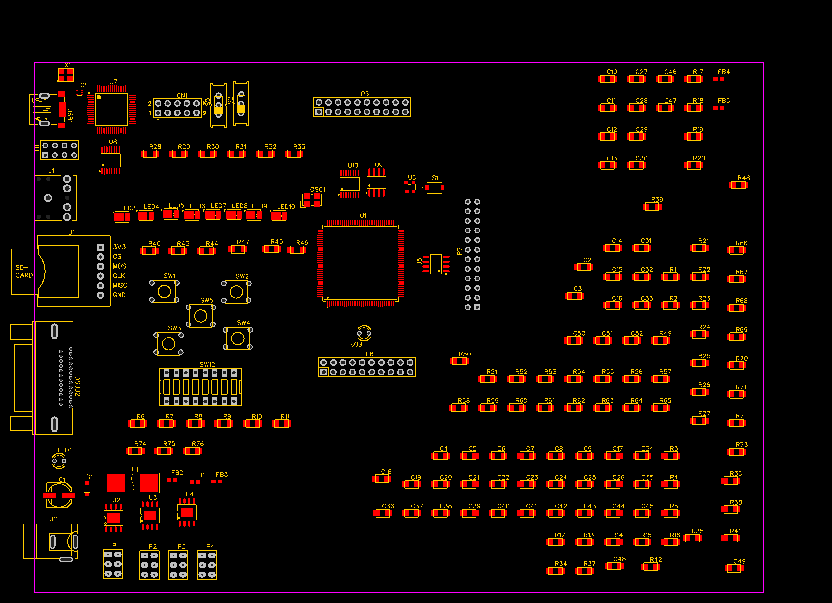

This is how the initial arrangement of components on the PCB looks like:

I will update the thread as I design the PCB.

Regards

I designed a simple development board with FPGA from GowinSemi - IC model: GW1N-LV9LQ144C6/I5. Here is link to mouser.com with this product:

https://www.mouser.com/ProductDetai...W1N-LV9LQ144C6-I5?qs=wnTfsH77Xs6N/yGezJZrJQ==

LittleBee |Products|GOWIN Semiconductor

LittleBee® family offers instant-on, non-volatile, low power, intensive I/O and small footprint FPGA (smallest as 2.4x2.3mm). It is also the first non-volatile FPGA with an embedded pSRAM in the industry, which further reduces the board space and enhances performance.

Tis is basic FPGA with 8640 LUT and 120 I/Os in LQFP-144 case. The amount of resources allow conduct experiments with Soft-CPU (for example with RISC-V soft-cores). My main goal was to design FPGA development which is cheap, but is suitable for beginners. Apart the FPGA itself the board is equipped with:

1) 24 MHz clock circuit

2) LDO voltage controllers and switches for configuring FPGA I/O Banks (three voltages: 3.3V , 2.5V and 1.2 V

3) FPGA Mode switches (for boot mode)

4) Setup circuitry (Reconfig, Done etc.)

5) FPGA reset circuit

6) USB to JTAG based on FTDI chip FT 2232HL (allowing programing by USB socket)

7) JTAG Header for alternating programming by "Gowin Cable" external programmer

8) Additional 32Mb SPI flash IC

9) 8MB of PSRAM (Pseudo RAM) alowing big frame-buffers

10) DSub15 VGA connector

11) 8 user LEDs

12) 8 DIP-Switches

13) 5 Push Buttons

14) TF (uSD) card module

15) Simple audio output

16) 59 I/O pins led out to the three goldpin connectors

I wanted the FPGA kit had the opportunity to program by USB socket and did not require expensive external programer (Gowin "USB Cable"), hence the use of the FTDI chip . I also wanted the FPGA board bring out a large number of I/O pins. I don't plan to output differential pins (LVDS) with impedance and length control on PCB. Here is finished schematic:

It remains to design the PCB.

This is how the initial arrangement of components on the PCB looks like:

I will update the thread as I design the PCB.

Regards