Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

Also check this thread!

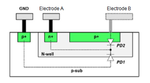

Also check this thread! The area of the parasitic diode (the n-well area) is bigger than the pd (the p+) area.

The area of the parasitic diode (the n-well area) is bigger than the pd (the p+) area.