shockingshockley

Member level 1

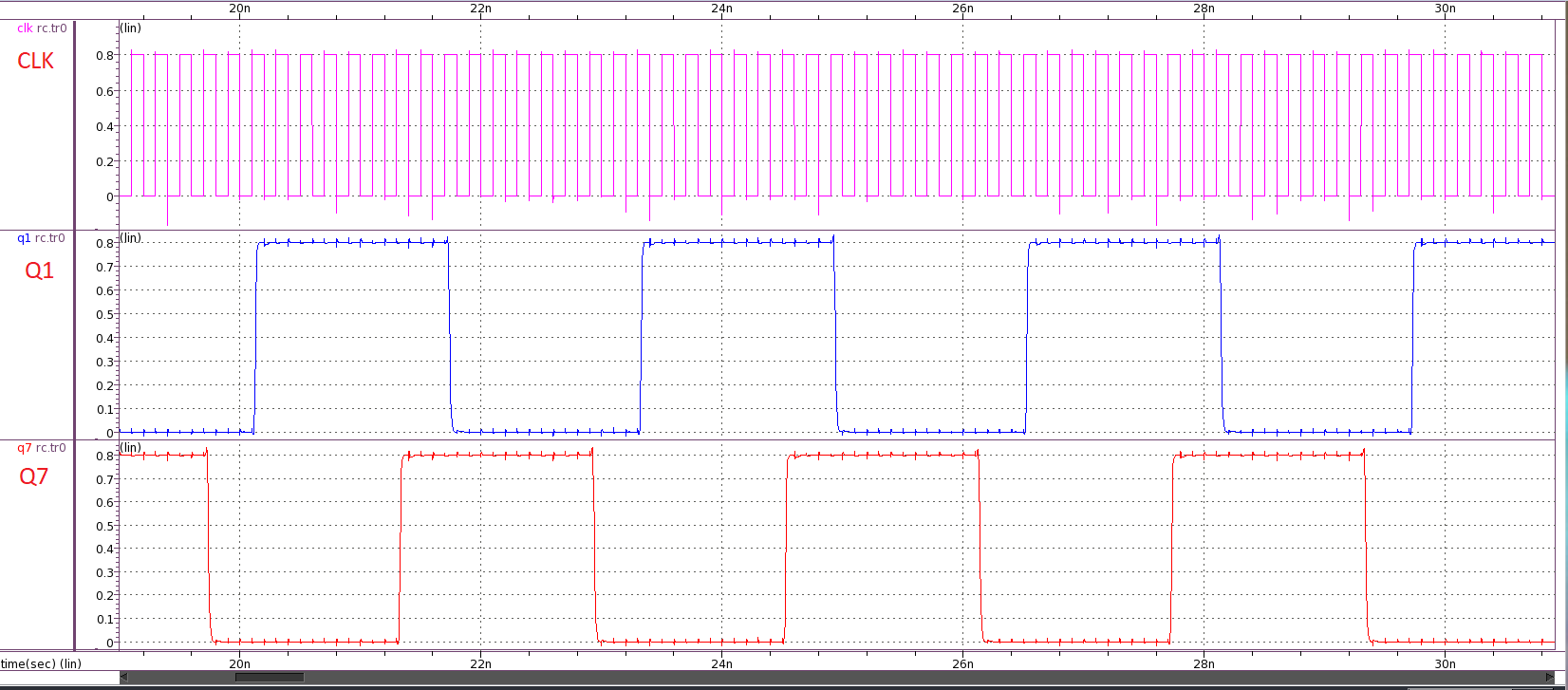

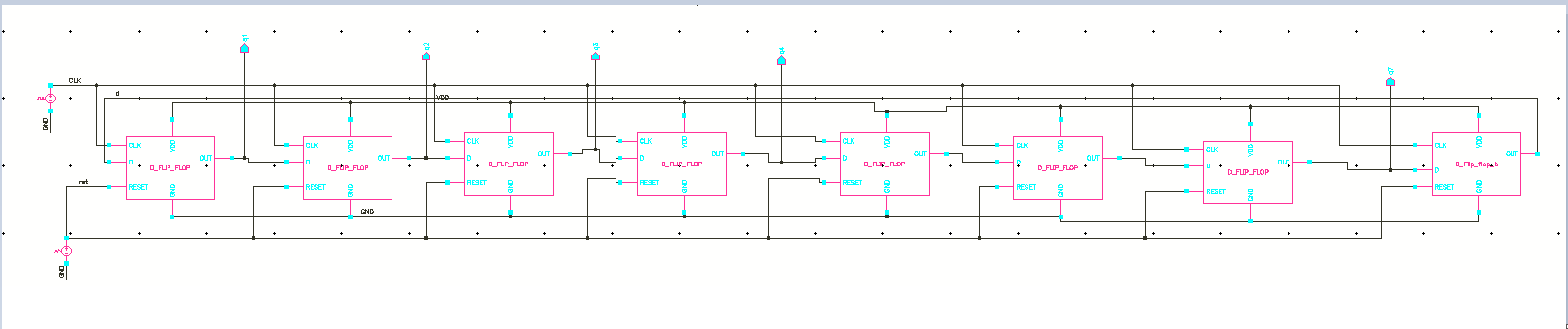

Hello. I am designing non overlapping circuit using counter. I would like Q1 and Q7 be non-overlap. Maybe increasing delay at Q7? Could you please provide me solution? WIll adding buffer helps? Or any suitable solution? THanks in advance.