Sonnenmann

Newbie level 5

Hi,

i design a fourth order delta sigma modulator in a feedforward CRFF structure.

Now i have finished the schematic implementation and tried to compare my results to my simulink model.

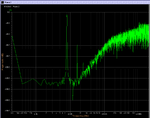

my problem is shown in the attached file. There are unwanted tones in the spectrum at fsig*2 and fsig*3 - how can i remove these tone?

Should i use dithering infront of the comparator? In my simulink model there are these peaks,too. But there are very very small.

fs=4MHZ fsig=8khz 20000 points fft - 1 Bit comparator - no matching problems in spice sim

i design a fourth order delta sigma modulator in a feedforward CRFF structure.

Now i have finished the schematic implementation and tried to compare my results to my simulink model.

my problem is shown in the attached file. There are unwanted tones in the spectrum at fsig*2 and fsig*3 - how can i remove these tone?

Should i use dithering infront of the comparator? In my simulink model there are these peaks,too. But there are very very small.

fs=4MHZ fsig=8khz 20000 points fft - 1 Bit comparator - no matching problems in spice sim