Ali263

Member level 1

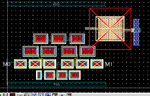

Dear all I am looking for doing triple well layout for an amplifier. I am using nmos_rf_6t . Though it seems easy for layout but but since there is a restrictions on Lenght and width so i had to use to use MULTIPLE Factor. For multiple factor 3, i get 3 segments for one nmos and each is kept in a separate deep nwell.

I was wondering if its right approach that each segment is placed in a separate deep n well or should i h connect all of them or can use one for them?

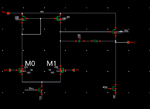

In picture M0, M1 has three multiple ,each with 30 fingers. M0 and M1 are also noted in layout

I was wondering if its right approach that each segment is placed in a separate deep n well or should i h connect all of them or can use one for them?

In picture M0, M1 has three multiple ,each with 30 fingers. M0 and M1 are also noted in layout