Mabrok

Full Member level 4

Hi,

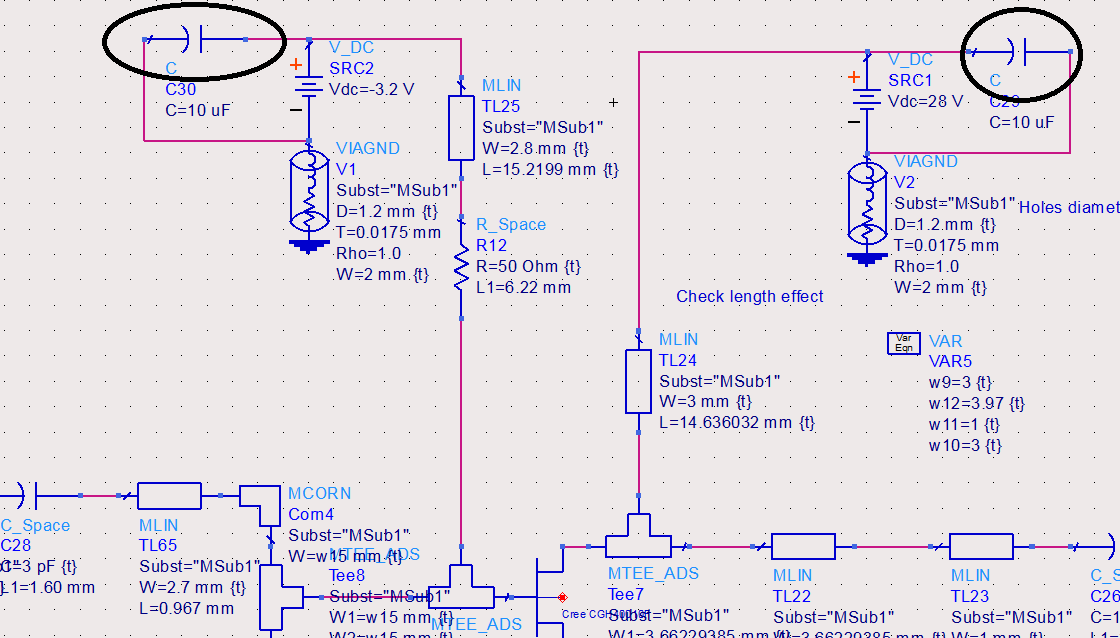

I can not see any effect on the simulation results after adding decoupling capacitor. Even when i tune the capacitance value, I can not see any effect. Is this normal?

I can not see any effect on the simulation results after adding decoupling capacitor. Even when i tune the capacitance value, I can not see any effect. Is this normal?