jdp721

Member level 2

- Joined

- Jun 29, 2009

- Messages

- 45

- Helped

- 4

- Reputation

- 8

- Reaction score

- 3

- Trophy points

- 1,288

- Activity points

- 1,621

Hi,

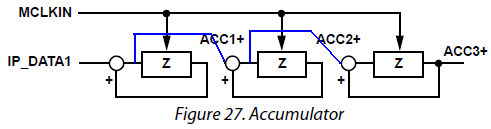

I am trying to realize a CIC decimation filter (for delta-sigma ADC) in Verilog.

I want to know whether to use NON-BLOCKING ASSIGNMENT <= or BLOCKING ASSIGNMENT = in Verilog implementation of the constituent integrators and differentiators.

E.g., for the integrator section (image below), commonly cited code is like:

always @ (posedge clk_in)

begin /*perform accumulation process*/

acc1 <= acc1 + ip_data;

acc2 <= acc2 + acc1;

acc3 <= acc3 + acc2;

end

I want to know if I can use Blocking assignment = instead of <= above - shouldn't that be better?

I am trying to realize a CIC decimation filter (for delta-sigma ADC) in Verilog.

I want to know whether to use NON-BLOCKING ASSIGNMENT <= or BLOCKING ASSIGNMENT = in Verilog implementation of the constituent integrators and differentiators.

E.g., for the integrator section (image below), commonly cited code is like:

always @ (posedge clk_in)

begin /*perform accumulation process*/

acc1 <= acc1 + ip_data;

acc2 <= acc2 + acc1;

acc3 <= acc3 + acc2;

end

I want to know if I can use Blocking assignment = instead of <= above - shouldn't that be better?