Jordon

Member level 1

- Joined

- Dec 25, 2022

- Messages

- 33

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 6

- Location

- Shanghai, China

- Activity points

- 261

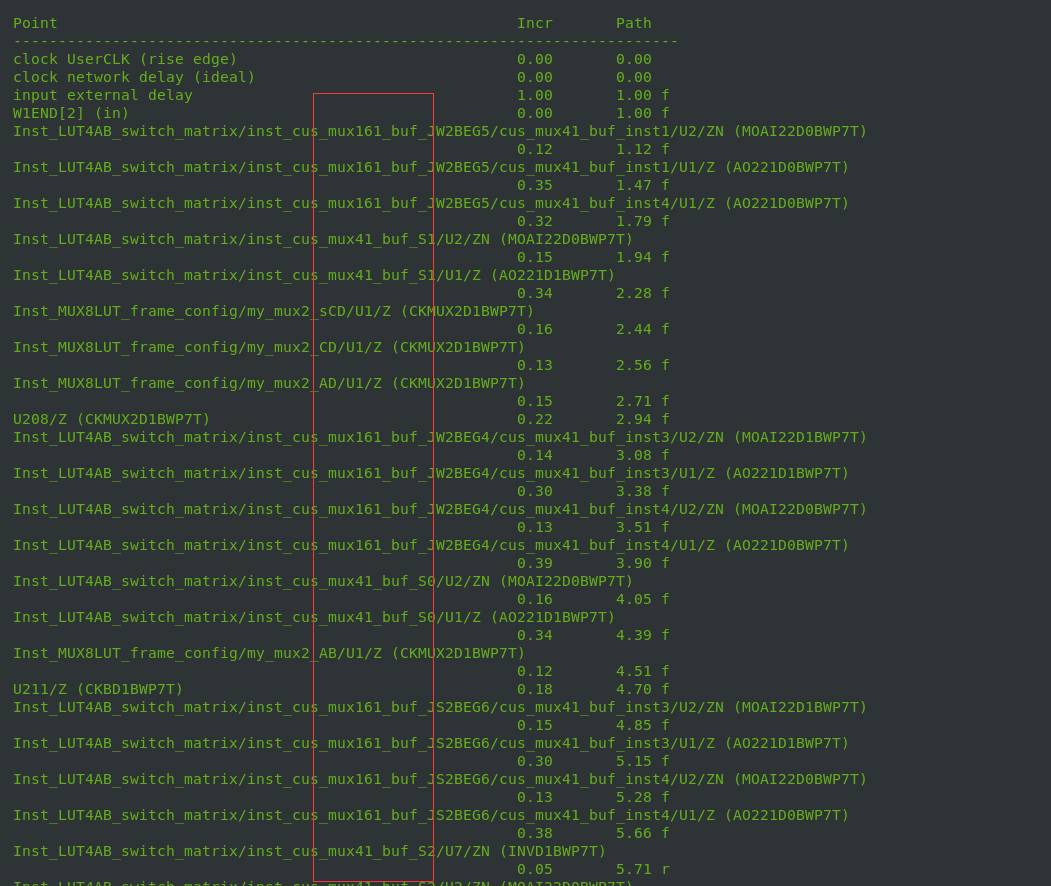

Hi, i am synthezing some modules in Design Compiler, coming this problem. take a example ,a module called lut4ab,its timing is not good for me. I check the path, it has many mux_buf which is customized defined(the same thing happened in other modules),

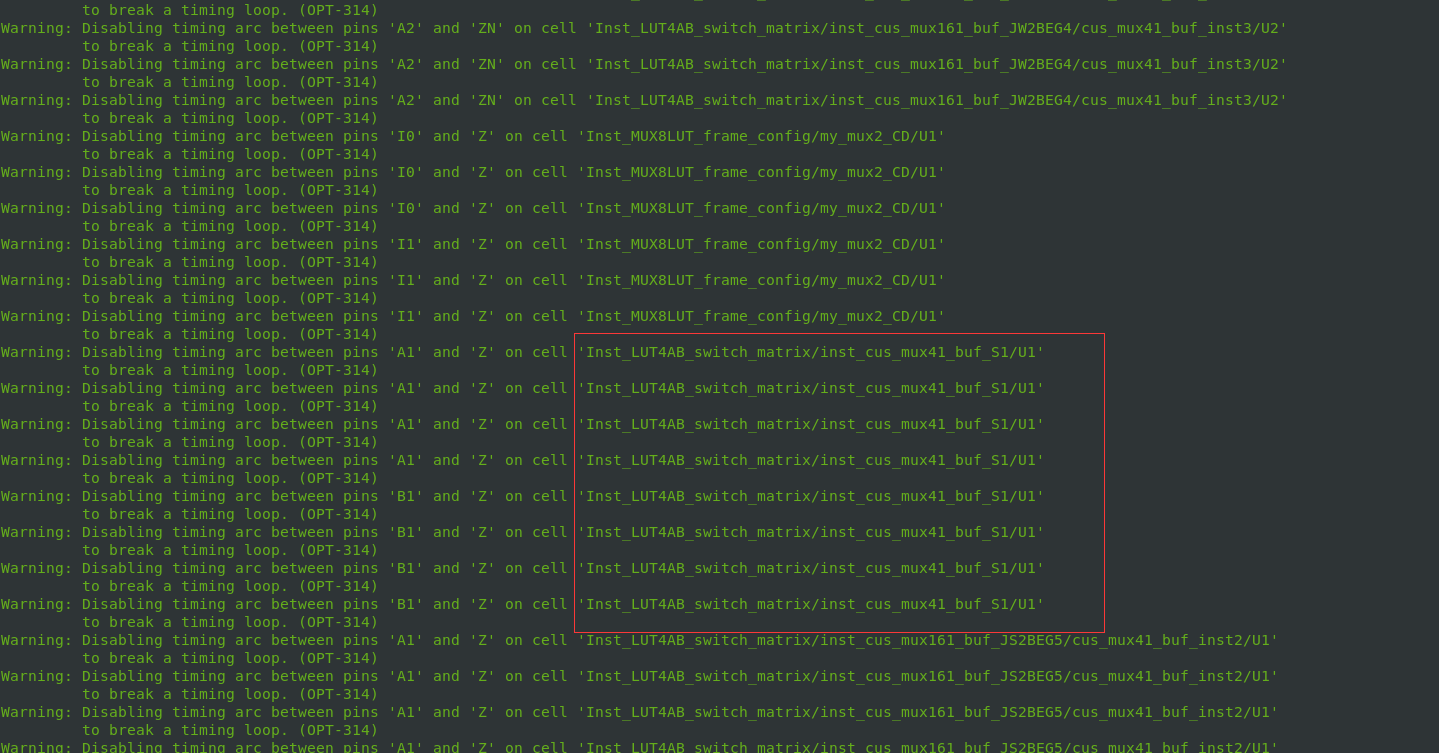

It report breaking timng arc loops, but i think no combinational loop exists in RTL codes.

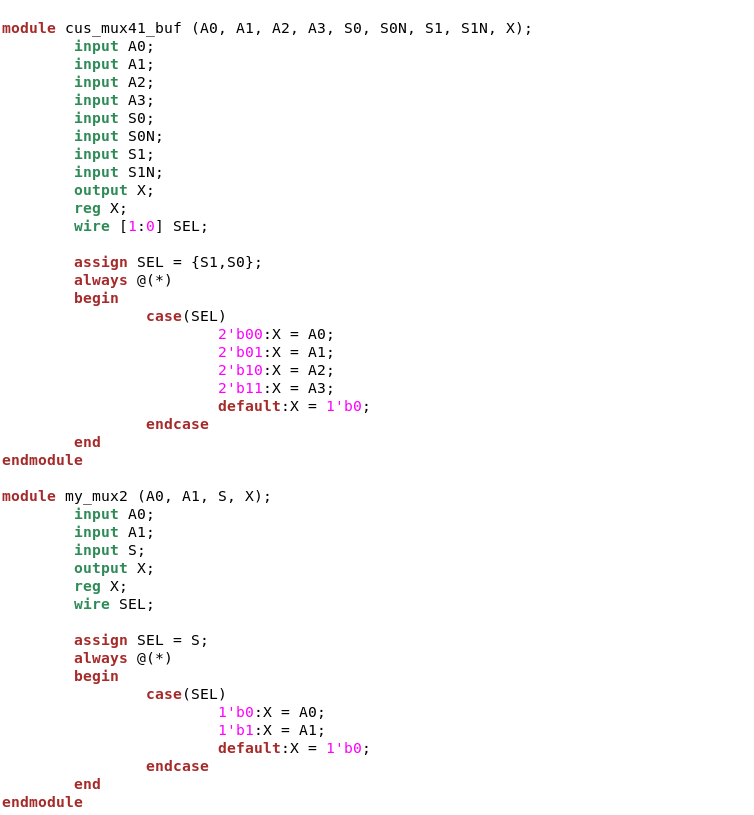

this is RTL codes

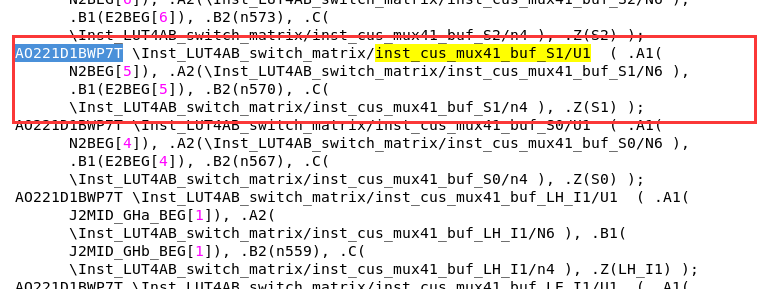

and i also check the GL codes

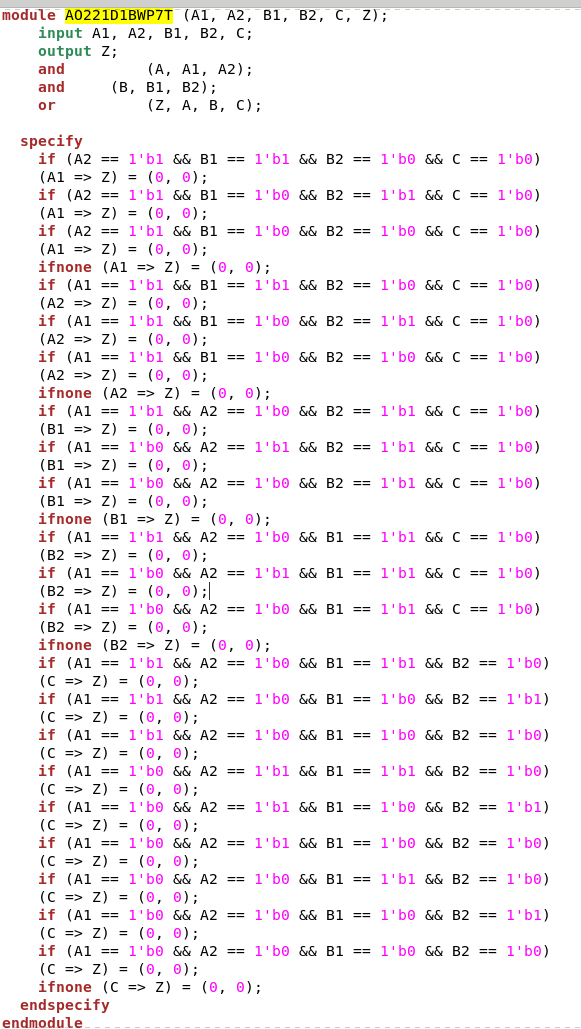

the unit define as below,

what should i do to slove the problem(synthesys timing is so bad and the timing loop) ?

It report breaking timng arc loops, but i think no combinational loop exists in RTL codes.

this is RTL codes

and i also check the GL codes

the unit define as below,

what should i do to slove the problem(synthesys timing is so bad and the timing loop) ?

Last edited: