zitty

Member level 2

Hello,

I want to design a VCO with current-starved inverters as delay cells.

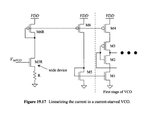

In the baker book they do a linearization of the input current as shown in the picture in the attachment.

M3 and M2 are sized with minimum l and w3/w2=2.

M4 and M1 work as current sources and they control the current flowing in the inverter.

I want to oscillate the VCO with a certain frequency fosc at Vdd/2. And I calculated the necessary current to achieve this frequency with the formula given in the book.

fosc=1/(N*2*td)=Id/(N*Ctot*Vdd)

where:

N=number of stages

td=inverter delay

Id= drain current of M4 and the others

Ctot=Cout+Cin=total capacitance on the drains of M2 and M3

Now I want to use the linearization circuit consistion of M5R, M6R, R and M5 and M6 to achieve a linear relation between Vin_VCO and this current.

M6 has the same sizes as M4 and M5 has the same sizes as M1.

MR6 and M5R are quite wide.

Now my problem. When I generate a current Id_M6R it will be mirrored into M6 and M4 right?

but how do I have to choose the transistorsizes that I will end up with the current that is necessary for the desired frequency fvco?

It seems that Id6 is not equal to Id4 any more because of the degradation of the drain voltages in M1 and M2? but I dont understand how this should work?

thanks for helping

I want to design a VCO with current-starved inverters as delay cells.

In the baker book they do a linearization of the input current as shown in the picture in the attachment.

M3 and M2 are sized with minimum l and w3/w2=2.

M4 and M1 work as current sources and they control the current flowing in the inverter.

I want to oscillate the VCO with a certain frequency fosc at Vdd/2. And I calculated the necessary current to achieve this frequency with the formula given in the book.

fosc=1/(N*2*td)=Id/(N*Ctot*Vdd)

where:

N=number of stages

td=inverter delay

Id= drain current of M4 and the others

Ctot=Cout+Cin=total capacitance on the drains of M2 and M3

Now I want to use the linearization circuit consistion of M5R, M6R, R and M5 and M6 to achieve a linear relation between Vin_VCO and this current.

M6 has the same sizes as M4 and M5 has the same sizes as M1.

MR6 and M5R are quite wide.

Now my problem. When I generate a current Id_M6R it will be mirrored into M6 and M4 right?

but how do I have to choose the transistorsizes that I will end up with the current that is necessary for the desired frequency fvco?

It seems that Id6 is not equal to Id4 any more because of the degradation of the drain voltages in M1 and M2? but I dont understand how this should work?

thanks for helping