bluesy

Junior Member level 1

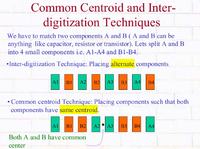

Hihi, may i know how to do interdigitize?? i have inserted two transistors one by one into layout . how should i do so that i can digitize both transistors together for matching? may i know that do i need to do modifications like adding transistor or others on my schematic? or i just need to leave schematic there having two transistors only for the current mirror? between, if my sizing of current mirror is 1:10 , can i use interdigitize or what should i do for the matching purpose?

For diffential amplifier, is that the best way is using common centriod? may i know how to fo the connection between them in schematic and layout as well. Besides, how should i do the sizing? For example, the total width two transistors of differential amplifier in my design is 20u each and i have fingered into 2 for the layout. Do i still need to do common centroid? If yes, how i do sizing for the transistors if i split the transistors to 4 instead of 2.

i am planning to do the matching as below:

A1 B1

B2 A2

thank you so much for your help

For diffential amplifier, is that the best way is using common centriod? may i know how to fo the connection between them in schematic and layout as well. Besides, how should i do the sizing? For example, the total width two transistors of differential amplifier in my design is 20u each and i have fingered into 2 for the layout. Do i still need to do common centroid? If yes, how i do sizing for the transistors if i split the transistors to 4 instead of 2.

i am planning to do the matching as below:

A1 B1

B2 A2

thank you so much for your help