keevvee

Newbie level 6

- Joined

- Feb 7, 2014

- Messages

- 11

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Location

- Norway

- Activity points

- 108

Dear all,

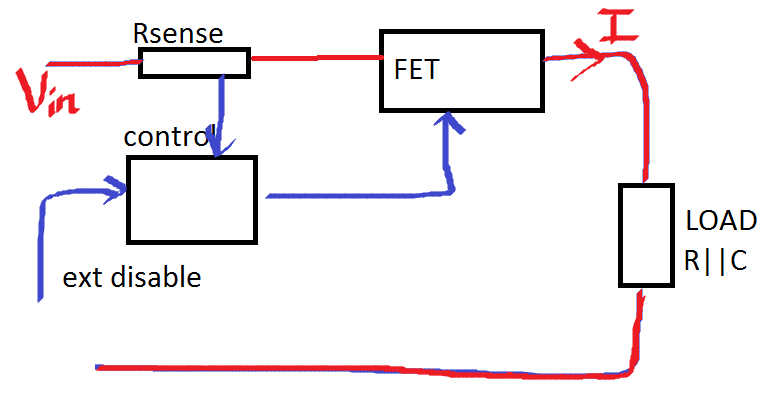

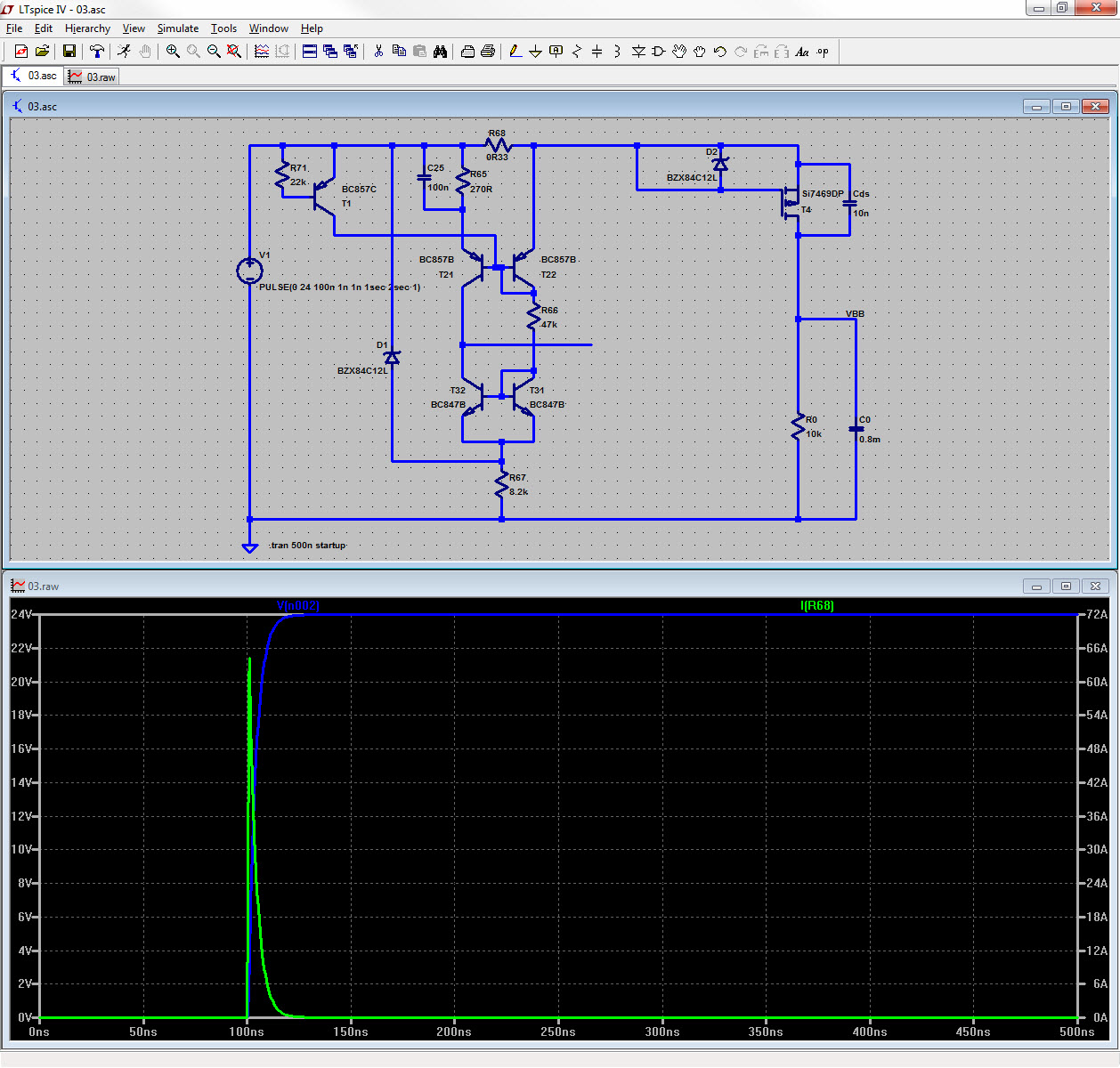

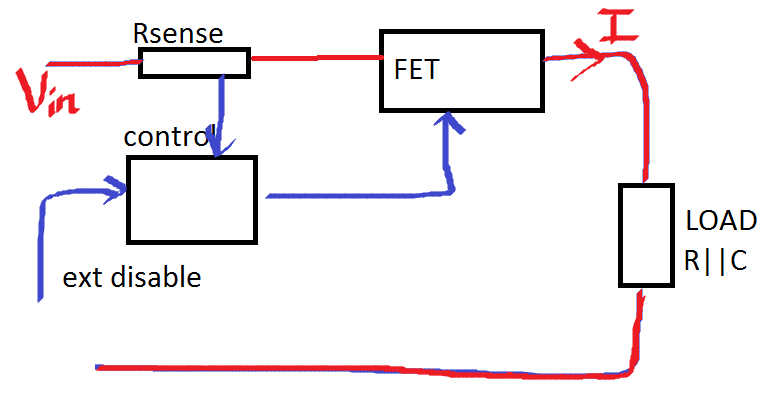

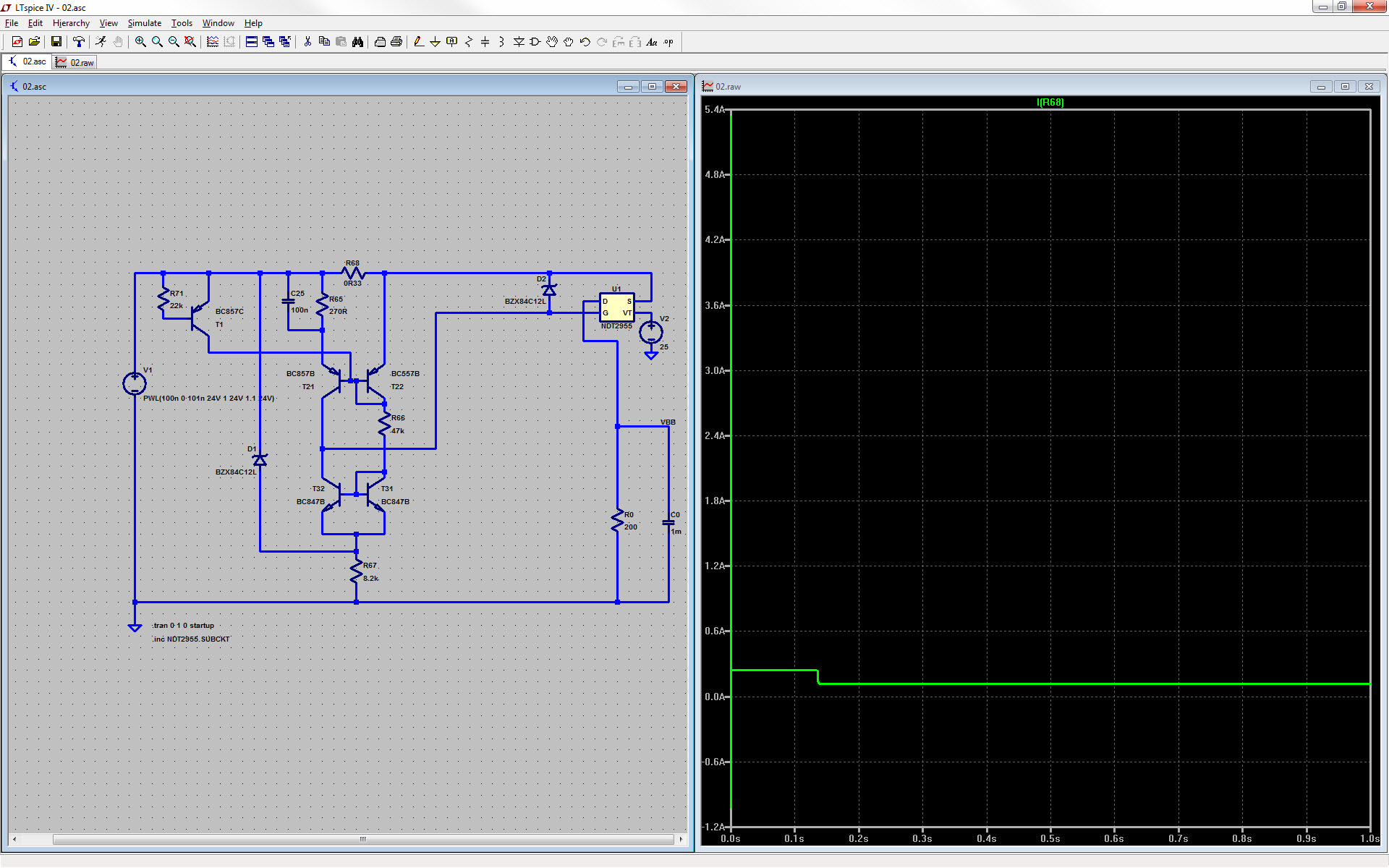

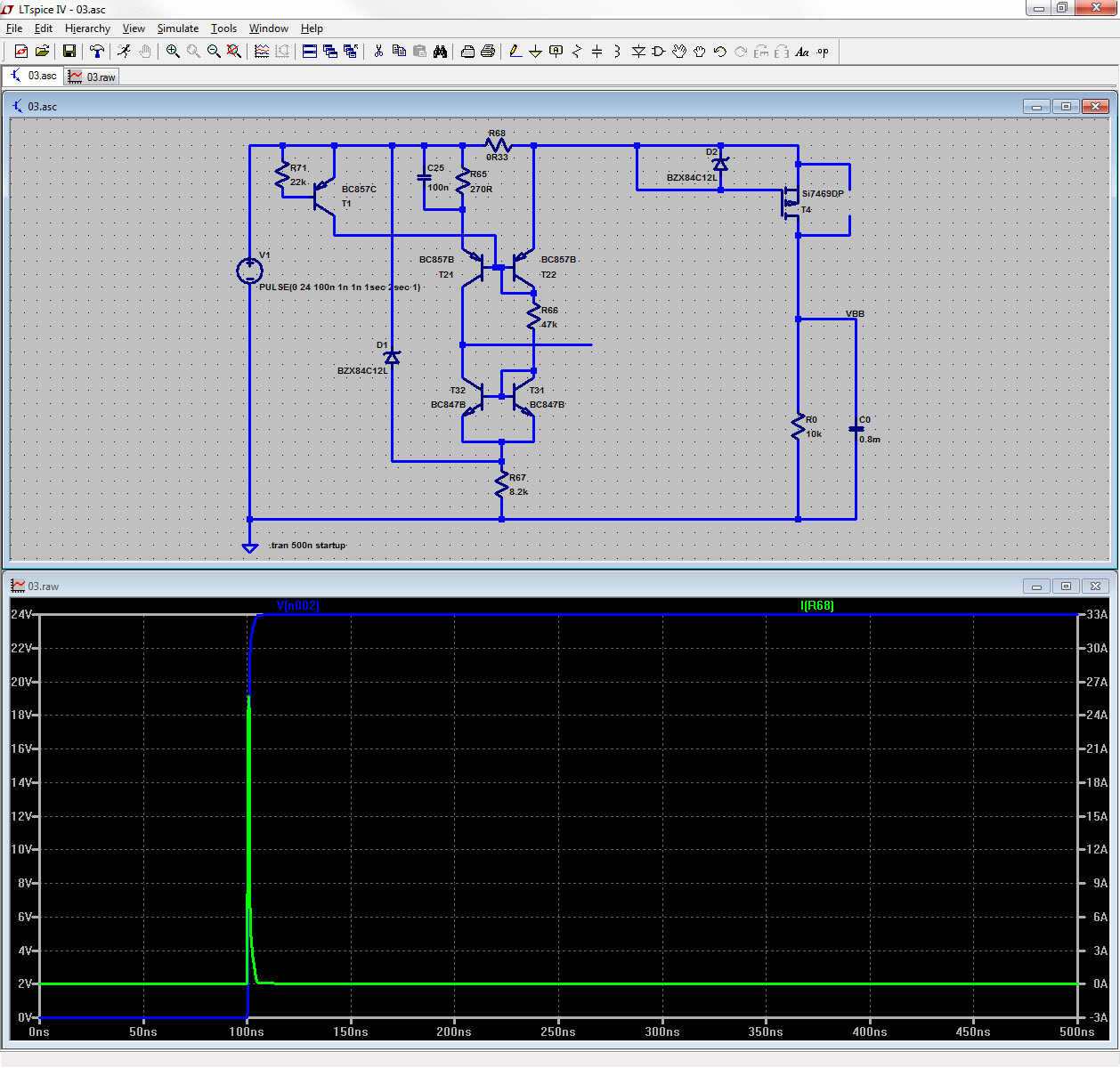

I'm struggling with an existing current limiter that looks like this:

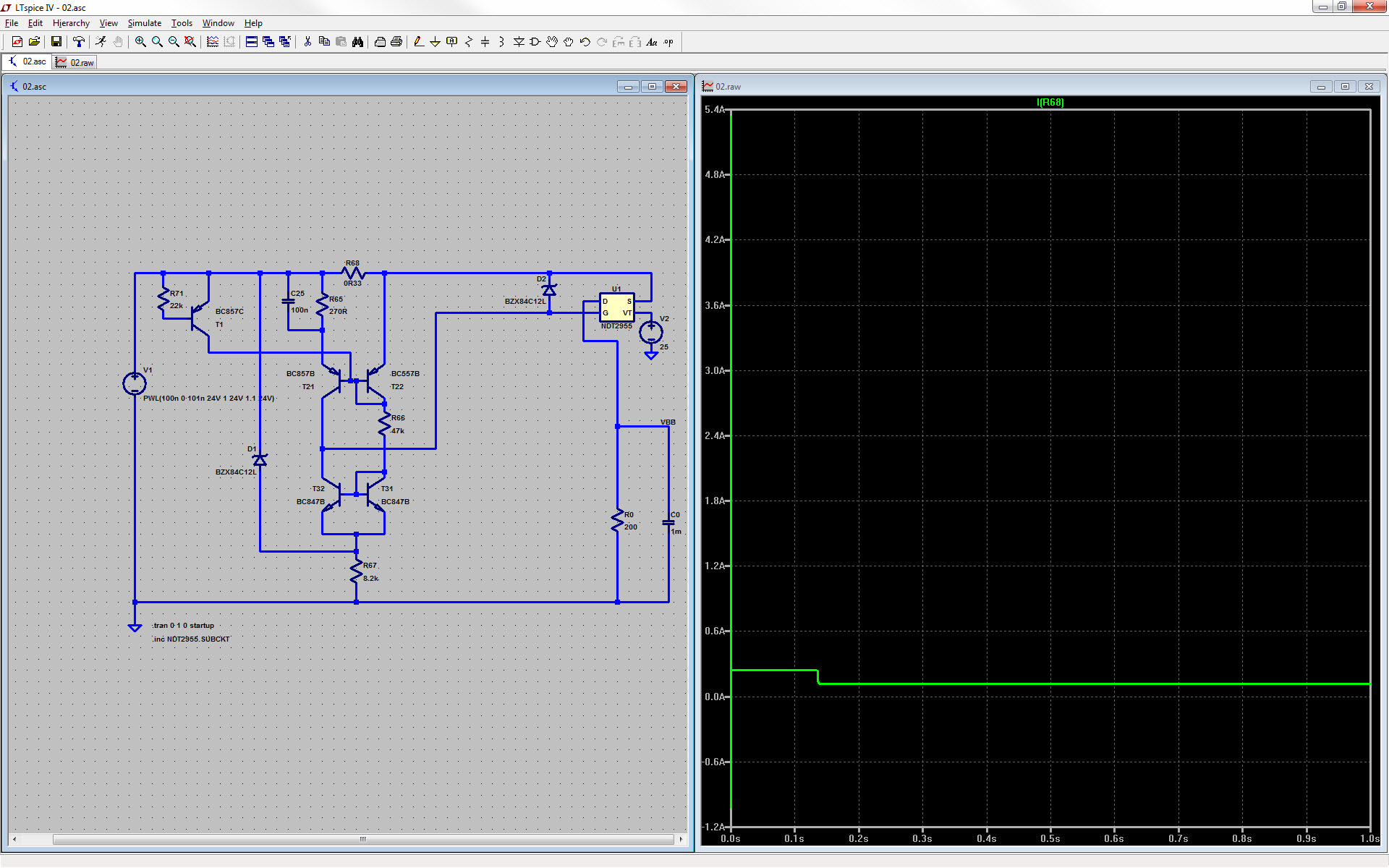

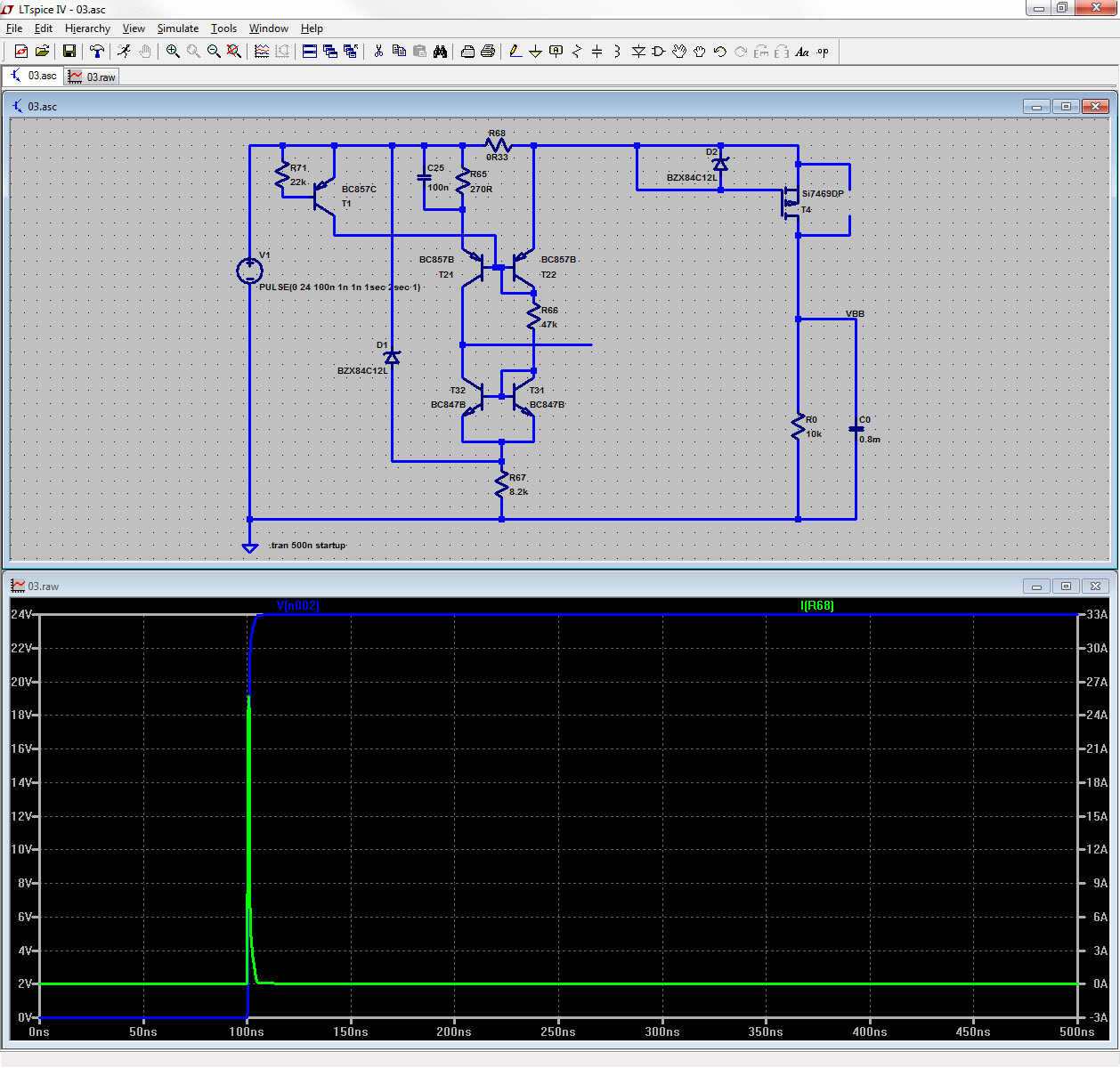

The problem I have is when Vin applied rapidly (high dv/dt) a current peak sneaks through.

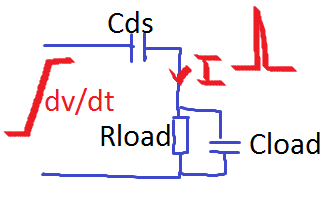

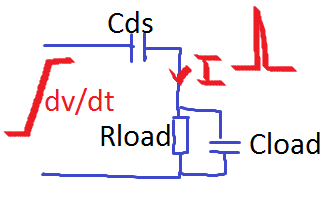

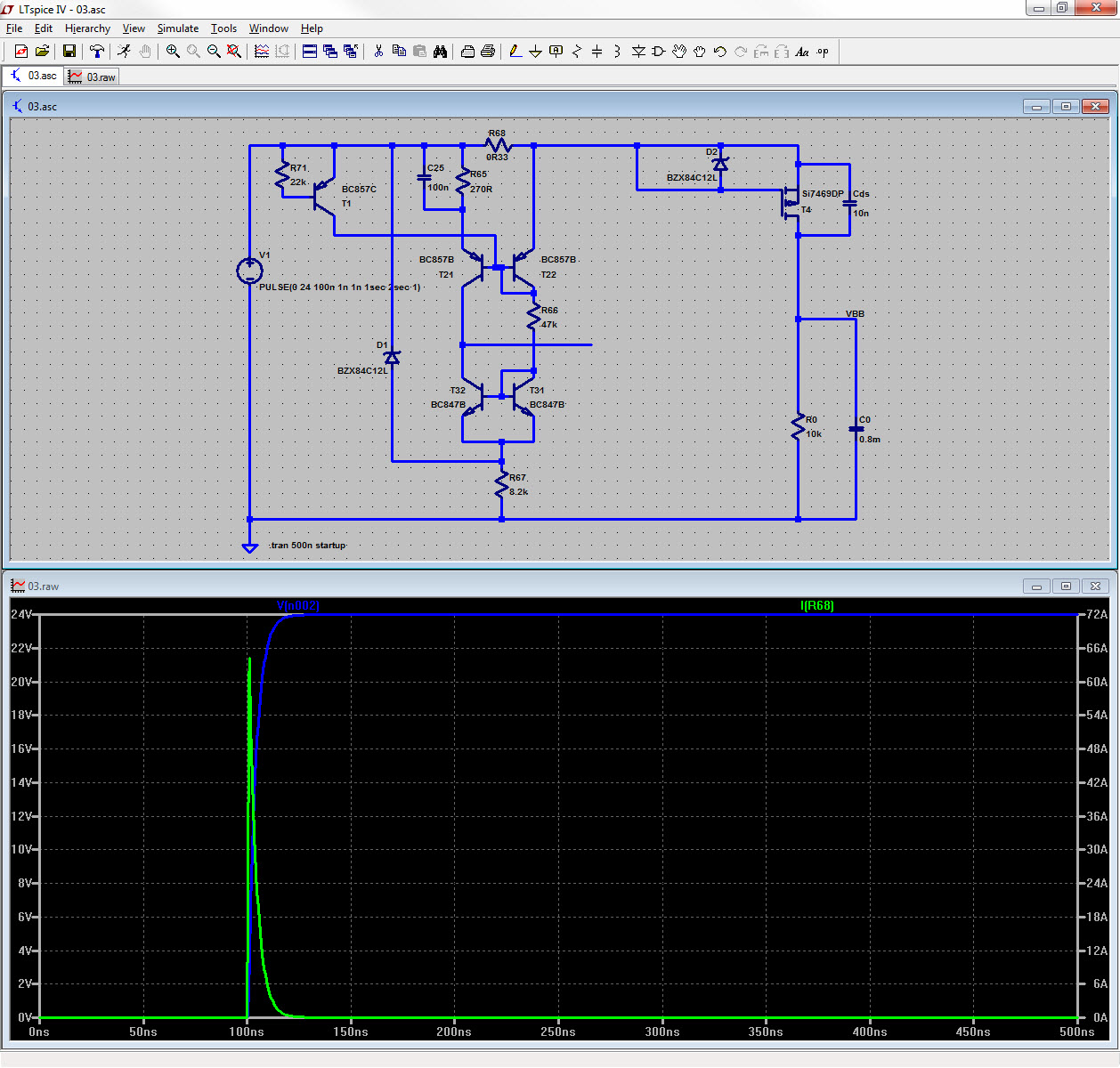

The meas & control is designed so the FET is OFF as long as the current is above the threshold, this is not a latching limiter, it's an analogue and I have exterminated the control circuit. No problem it's following from the first picosends. My theory is the FET capacitance (D-S), like this:

I even made a simulation in which the FET always biased OFF and the current peak is still present.

Furthermore I have added a CAP in parallel to the FET and the current peak was higher.

After this short transient, the current limiter is working properly, limiting the current until the Cload is charged.

Do you agree with my analysis?

Is there anything to removed the transient current in the first nanoseconds?

I know a nice circuit would be a one that has a RES limiting the current by default and then switching after the power on to a direct conn. but the circuit it already in market and I'm wondering how to reduce the problem with minimum effort.

Thank you in advance.

I'm struggling with an existing current limiter that looks like this:

The problem I have is when Vin applied rapidly (high dv/dt) a current peak sneaks through.

The meas & control is designed so the FET is OFF as long as the current is above the threshold, this is not a latching limiter, it's an analogue and I have exterminated the control circuit. No problem it's following from the first picosends. My theory is the FET capacitance (D-S), like this:

I even made a simulation in which the FET always biased OFF and the current peak is still present.

Furthermore I have added a CAP in parallel to the FET and the current peak was higher.

After this short transient, the current limiter is working properly, limiting the current until the Cload is charged.

Do you agree with my analysis?

Is there anything to removed the transient current in the first nanoseconds?

I know a nice circuit would be a one that has a RES limiting the current by default and then switching after the power on to a direct conn. but the circuit it already in market and I'm wondering how to reduce the problem with minimum effort.

Thank you in advance.