celebrevida

Member level 2

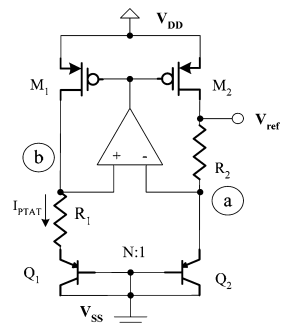

I am trying to design a CTAT voltage generator such that:

Vout = mx + b

where I can control both m and b separately.

The closest I can come up with is using the CTAT voltage of a bandgap reference circuit.

If R2 is actually several transistors in series, then I can select different taps "inside" R2 using an analog mux and thus select slope "m".

And we can see that:

As I select the slope "m", I am also changing "b" at the same time!

How can I design a CTAT voltage reference in which both "m" and "b" are independently selectable?

Thanks for any help!

Vout = mx + b

where I can control both m and b separately.

The closest I can come up with is using the CTAT voltage of a bandgap reference circuit.

If R2 is actually several transistors in series, then I can select different taps "inside" R2 using an analog mux and thus select slope "m".

And we can see that:

- Node (a) would have the most negative slope (m_maxneg)

- Node Vref would have a flat slope. (m_0)

- All nodes between Vref and a would have a slope between m_0 and (m_maxneg).

As I select the slope "m", I am also changing "b" at the same time!

How can I design a CTAT voltage reference in which both "m" and "b" are independently selectable?

Thanks for any help!