geozog86

Member level 3

Hello everyone!

I started this post in Analog Circuit, but i was advised to move it here.

Task: i have to create a continuous time comparator, i.e., i don't have a fast clock to check periodically the situation (like in the most common AD comparator) but i want just to hook up one input to a threshold (low, around 500mV), and the other to a slow rising voltage (0 to 0.5 in 15usec) and then i want it to change state. The next stage is a memory-let's say a flip flop. And the crucial point is temperature stability. I should be changing state in the memory at the same time moment, no matter what temperature i'm using (-30 to 90), so i care about the moment i'm crossing the threshold of the memory to be constant: i don't care if the comparator will start changing state earlier, with a different slope or whatever.

Questions:

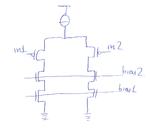

1)Is my topology going to be just an amplifier that will saturate? Is that the "basic comparator topology"?

2)Which topology is benefitial to provide symmetrical behaviour in rising slope and falling slope?

3)See below: first approach is this simple topology of an amplifier. I am showing you the results of the two outputs in room temperature. I get it that one output is what i want and the other is worse, due to the different inputs that they see. But when i'm sweeping from -30 to 90 degrees you see the other plot, with 3 temperatures. You see that in 90 it's working "faster", changing state earlier, room temperature it's slower, and in -30 it doesn't even work!

Of course this stage has only 40dB of gain, and i guess my final topology will have to have a lot more, but i'm just asking why is this happening? Are there "temperature resistant" amplifier/comparator topologies?

THank you all very much

PS i'm using an old technology, 700nm, and a supply of 1.8V

I started this post in Analog Circuit, but i was advised to move it here.

Task: i have to create a continuous time comparator, i.e., i don't have a fast clock to check periodically the situation (like in the most common AD comparator) but i want just to hook up one input to a threshold (low, around 500mV), and the other to a slow rising voltage (0 to 0.5 in 15usec) and then i want it to change state. The next stage is a memory-let's say a flip flop. And the crucial point is temperature stability. I should be changing state in the memory at the same time moment, no matter what temperature i'm using (-30 to 90), so i care about the moment i'm crossing the threshold of the memory to be constant: i don't care if the comparator will start changing state earlier, with a different slope or whatever.

Questions:

1)Is my topology going to be just an amplifier that will saturate? Is that the "basic comparator topology"?

2)Which topology is benefitial to provide symmetrical behaviour in rising slope and falling slope?

3)See below: first approach is this simple topology of an amplifier. I am showing you the results of the two outputs in room temperature. I get it that one output is what i want and the other is worse, due to the different inputs that they see. But when i'm sweeping from -30 to 90 degrees you see the other plot, with 3 temperatures. You see that in 90 it's working "faster", changing state earlier, room temperature it's slower, and in -30 it doesn't even work!

Of course this stage has only 40dB of gain, and i guess my final topology will have to have a lot more, but i'm just asking why is this happening? Are there "temperature resistant" amplifier/comparator topologies?

THank you all very much

PS i'm using an old technology, 700nm, and a supply of 1.8V