Amr Wael

Member level 5

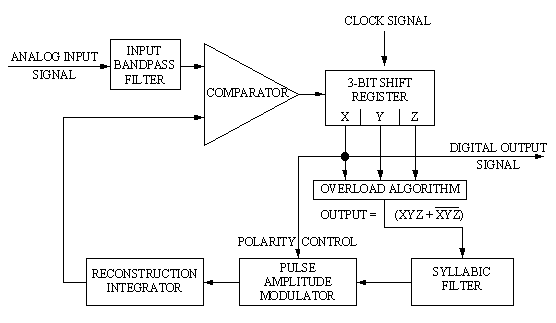

Hello , I am trying to understand how does CVSD Modulator works. The block diagram of the CVSD is below , I understand that the overload algorithm detects whether the previous 3 bits of the modulated signal are all 1s or all zeros. and based on this signal is controls the charging or discharging of the syllabic filter. What I don't understand is what's the relation or the equation that describes the relation between the output of the syllabic filter and the PAM. I understand the PAM is going to decrease or increase the signal by a step size of delta based on the polarity control signal. But what's the relation between the step size delta and between the output of the syllabic filter?

Thank you very much in advance.

Thank you very much in advance.