ranaya

Advanced Member level 4

Dear All,

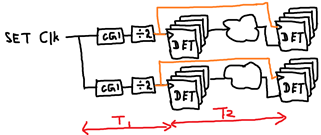

I have a design that looks like below. The design first receives a single edge triggered clock and through some clock gates, this clock signal is divided by 2 to convert it to a double edge triggered (DET) signal. The idea here is to incorporate DET FFs in a larger digital design. Since standard CAD tools do not understand DET behaviour, the placement of DETs after the initial synthesis is customly made. So that the timing graphs can be re-generated using DET timing in design compiler.....

How should we specify the sdc constraints for the clock tree at PnR stage ?

Thanks

I have a design that looks like below. The design first receives a single edge triggered clock and through some clock gates, this clock signal is divided by 2 to convert it to a double edge triggered (DET) signal. The idea here is to incorporate DET FFs in a larger digital design. Since standard CAD tools do not understand DET behaviour, the placement of DETs after the initial synthesis is customly made. So that the timing graphs can be re-generated using DET timing in design compiler.....

How should we specify the sdc constraints for the clock tree at PnR stage ?

Thanks